January 2020

# Single Package MIL-STD-1553 / MIL-STD-1760 3.3V BC / MT / RT with Integrated Transformers

#### **GENERAL DESCRIPTION**

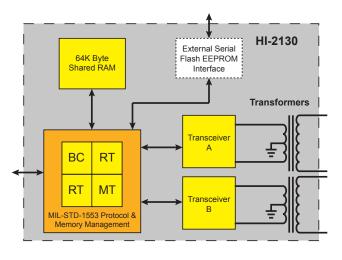

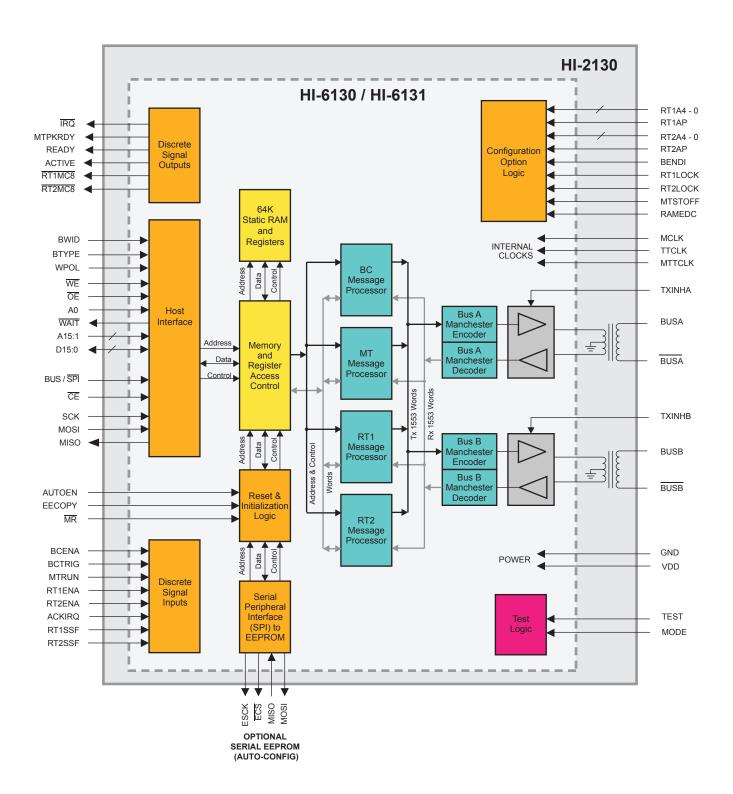

The HI-2130 provides a 3.3V fully integrated interface between a host processor and a MIL-STD-1553 / MIL-STD-1760 bus. It combines the functionality of Holt's HI-6130 16-bit parallel bus interface and HI-6131 SPI devices, integrating MIL-STD-1553 protocol logic, dual transceivers and dual transformers in a single compact 15 x 15 x 4.4 mm package; the smallest 1553 terminal solution with integrated magnetics in a single package. Both RoHS compliant and Sn/Pb configurations are available, giving customers a solution for tin-lead assemblies while avoiding expensive re-balling.

The device includes the entire signal I/O set of HI-6130 and HI-6131, with the addition of a new input signal for selecting parallel bus or SPI host interface. Two pairs of transformer output signals connect directly to the MIL-STD-1553 Bus A and Bus B stubs.

The part is available in Industrial -40°C to +85°C, or Extended, -55°C to +125°C temperature ranges.

Refer to the HI-6130 datasheet for full functional description and operation.

#### **FEATURES**

- Combined functionality of HI-6130 and HI-6131 in a single package with integrated transformers

- Smallest footprint MIL-STD-1553 solution available (includes transformers)

- Low profile package solution suitable for PMC and XMC applications

- Extended temperature range, -55°C to +125°C

- Hermetically sealed die option (MSL 1) available

- Less expensive than traditional multi-chip modules

- · DO-254 certifiable

- Concurrent multi-terminal operation (BC, MT, 1 or 2 independent RTs)

- Two host interface options in one package: 16-bit parallel bus or 4-wire SPI

- 64K bytes on-chip RAM with error detection/ correction option

- Autonomous terminal operation requires minimal host intervention

- Shared MIL-STD-1553 bus interface reduces circuit complexity and circuit board area.

- Fully programmable Bus Controller with 28 op code instruction set

- Simple Monitor Terminal (SMT) Mode records commands and data separately, with 16-bit or 48-bit time tagging

- IRIG Monitor Terminal (IMT) Mode supports IRIG-106 Chapter 10 packet format. Complete IRIG-106 data packets including full packet headers and trailers can be generated

- Independent time-tag counters for all terminals with 32-bit option for Bus Controller and 48-bit option for Monitor Terminal

- 64-Word Interrupt Log Buffer queues the most recent 32 interrupts. Hardware-assisted interrupt decoding quickly identifies interrupt sources

- Built-in self-test for protocol logic, digital signal paths and internal RAM

- Optional self-initialization at reset uses external serial EEPROM

- Two temperature ranges: -40°C to +85°C, or -55°C to +125°C

# **BLOCK DIAGRAM**

#### **PIN DIAGRAM**

#### Top View

|   | 11         | 10          | 9          | 8          | 7          | 6          | 5            | 4           | 3           | 2          | 1         |   |

|---|------------|-------------|------------|------------|------------|------------|--------------|-------------|-------------|------------|-----------|---|

| L | RAM<br>EDC | DATA<br>14  | DATA<br>11 | DATA<br>9  | DATA<br>4  | RT1<br>SSF | MTPKT<br>RDY | RT1<br>MC8  | nIRQ        | B<br>TYPE  | BENDI     | L |

| K | nCE        | DATA<br>12  | DATA<br>10 | AUTO<br>EN | DATA<br>6  | VDD        | AC-<br>TIVE  | ACK<br>IRQ  | DATA<br>2   | WPOL       | nBUS<br>A | K |

| J | MODE       | BC<br>TRIG  | DATA<br>13 | TX<br>INHA | DATA<br>7  | DATA<br>5  | READY        | TEST        | DATA<br>0   | DATA<br>1  | nBUS<br>A | J |

| Н | MISO       | DATA<br>15  | MOSI       | TX<br>INHB | DATA<br>8  | DATA<br>3  | RT2<br>MC8   | MTST<br>OFF | RT1<br>LOCK | DNC        | BUS<br>A  | Н |

| G | nWAIT      | SCLK        | nOE        | VDD        | GND        | VDD        | GND          | VDD         | BC<br>ENA   | DNC        | BUS<br>A  | G |

| F | nWE        | BUS<br>nSPI | MCLK       | GND        | VDD        | GND        | VDD          | GND         | VDD         | DNC        | DNC       | F |

| Е | RT1<br>A2  | RT1<br>A0   | RT1<br>A1  | VDD        | GND        | VDD        | GND          | VDD         | RT2<br>ENA  | DNC        | BUS<br>B  | Е |

| D | nMR        | RT1<br>A3   | RT1<br>A4  | ADDR<br>8  | nECS       | ADDR<br>10 | RT2<br>LOCK  | RT2<br>A0   | RT2<br>A1   | DNC        | BUS<br>B  | D |

| С | ADDR<br>0  | RT1<br>ENA  | ADDR<br>2  | E<br>MOSI  | GND        | EE<br>COPY | MT<br>RUN    | RT2<br>A2   | RT2<br>A3   | ADDR<br>14 | nBUS<br>B | С |

| В | ADDR<br>1  | ADDR<br>3   | ADDR<br>4  | ADDR<br>6  | TT<br>CLK  | VDD        | ESCK         | RT2<br>SSF  | ADDR<br>13  | ADDR<br>15 | nBUS<br>B | В |

| Α | ADDR<br>5  | RT1<br>AP   | E<br>MISO  | ADDR<br>7  | MTT<br>CLK | ADDR<br>9  | ADDR<br>11   | RT2<br>AP   | RT2<br>A4   | ADDR<br>12 | BWID      | Α |

|   | 11         | 10          | 9          | 8          | 7          | 6          | 5            | 4           | 3           | 2          | 1         |   |

#### See HI-6130 datasheet for a full Pin Description.

#### Notes:

- a. DNC: Do Not Connect.

- b. All balls denoted VDD **must** be connected to 3.3V DC power.

- c. All balls denoted GND must be connected to circuit ground.

- d. BUS/nSPI (F10) selects 16-bit wide parallel bus or SPI operation (see Section "Selection of Host Interface" on page 4).

- e. nCE: The chip enable signal is shared between 16-bit parallel and SPI host interfaces (SPI Slave Select).

# **OPERATION**

Refer to the HI-6130 datasheet for detailed operation and register description.

# **Selection of Host Interface**

The host interface is selected using the SPI/ $\overline{\text{BUS}}$  pin.

- BUS/SPI pin set to logic "1": Selects 16-bit parallel bus host interface

- BUS/SPI pin reset to logic "0": Selects SPI host interface

# **ELECTRICAL CHARACTERISTICS**

# **Absolute Maximum Ratings**

| Supply voltage (V <sub>DD</sub> ) | -0.3 V to +5.0 V |

|-----------------------------------|------------------|

| Logic input voltage range         | -0.3 V to +3.6 V |

| Receiver differential voltage     | 10 Vp-p          |

| Solder Temperature (reflow)       | 245°C            |

| Junction Temperature              | 175°C            |

| Storage Temperature               | -65°C to +150°C  |

# **Recommended Operating Conditions**

| Operating Supply voltage (V <sub>DD</sub> ) | 3.3 VDC ± 5%                      |  |  |

|---------------------------------------------|-----------------------------------|--|--|

| Operating Temperature Range                 |                                   |  |  |

| Industrial<br>Extended                      | -40°C to +85°C<br>-55°C to +125°C |  |  |

NOTE: Stresses above absolute maximum ratings or outside recommended operating conditions may cause permanent damage to the device. These are stress ratings only. Operation at the limits is not recommended.

#### **DC Electrical Characteristics**

$V_{_{\rm DD}}$  = 3.3V, GND = 0V,  $T_{_{\rm A}}$  = Operating Temperature Range (unless otherwise stated)

| Banamatana                                   | Ol               | Took Conditions                                                                         | I    | Limits |      | 11:4            |

|----------------------------------------------|------------------|-----------------------------------------------------------------------------------------|------|--------|------|-----------------|

| Parameters                                   | Symbol           | Test Conditions                                                                         | Min  | Тур    | Max  | Unit            |

| Operating Voltage                            | V <sub>DD</sub>  |                                                                                         | 3.15 | 3.3    | 3.45 | V               |

|                                              | I <sub>CC1</sub> | Not Transmitting                                                                        | -    | 40     | 50   | mA              |

| Power Supply Current See Note 1 on next page | I <sub>CC2</sub> | Continuous supply current while one bus transmits @ 100% duty cycle, 78Ω resistive load | -    | 720    | 760  | mA              |

| Power Dissipation                            | PD <sub>1</sub>  | Not Transmitting                                                                        | -    | 132    | 172  | mW              |

| See Note 2 on next page                      | PD <sub>2</sub>  | Transmit one bus @ 100% duty cycle, 78Ω resistive load                                  | -    | 0.85   | 1.04 | W               |

| Input Voltage (High)                         | V <sub>IH</sub>  | Digital Inputs                                                                          | 70%  | -      | -    | V <sub>DD</sub> |

| Input Voltage (Low)                          | V <sub>IL</sub>  | Digital Inputs                                                                          | -    | -      | 30%  | V <sub>DD</sub> |

| Input Current (High): inputs with pull-down. | I <sub>IH</sub>  | Digital Inputs (each digital input pulled high)                                         | -    | -      | 100  | μА              |

| Input Current (High): inputs with pull-up.   | I <sub>IH</sub>  | Digital Inputs (each digital input pulled high)                                         | +1   | -      | -    | μА              |

| Parameters                                 |                           |                   | To ad O and Hilliams                             | Limits |     |      | 1114            |

|--------------------------------------------|---------------------------|-------------------|--------------------------------------------------|--------|-----|------|-----------------|

| Paramete                                   | ers                       | Symbol            | Test Conditions                                  | Min    | Тур | Max  | Unit            |

| Input Current (Low) inputs with pull-up.   |                           | I <sub>IL</sub>   | Digital Inputs (each digital input pulled low)   | -      | -   | -100 | μA              |

| Input Current (Low) inputs with pull-down. |                           | I                 | Digital Inputs (each digital input pulled low)   | -1     | -   | -    | μA              |

| Output Voltage (High)                      |                           | V <sub>OH</sub>   | I <sub>OUT</sub> = -1.0mA, Digital outputs       | 90%    | -   | -    | V <sub>DD</sub> |

| Output Voltage (Low)                       |                           | V <sub>OL</sub>   | I <sub>OUT</sub> = 1.0mA, Digital outputs        | -      | -   | 10%  | V <sub>DD</sub> |

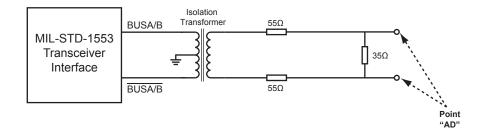

| RECEIVER (Measured at Point "              | AD" in Figure 7 unless    | otherwise sp      | pecified)                                        |        |     |      |                 |

| Input Resistance                           |                           | R <sub>IN</sub>   | Differential                                     | 20     | -   | -    | kΩ              |

| Input Capacitance                          |                           | C <sub>IN</sub>   | Differential                                     | -      | -   | 5    | pF              |

| Common Mode Rejection Ratio                |                           | CMRR              |                                                  | 40     | -   | -    | dB              |

| Input Level                                |                           | V <sub>IN</sub>   | Differential                                     | -      | -   | 9    | Vp-p            |

| Input Common Mode Voltage                  |                           | V <sub>ICM</sub>  |                                                  | -5     | -   | +5   | V-pk            |

| Threshold Voltage                          | Detect                    | V <sub>THD</sub>  | 1 MHz Sine Wave (Measured                        | 1.15   | -   | 20.0 | Vp-p            |

| (Direct-Coupled)                           | No Detect                 | V <sub>THND</sub> | at Point "AD" in Figure 7)                       | 1      | -   | 0.28 | Vp-p            |

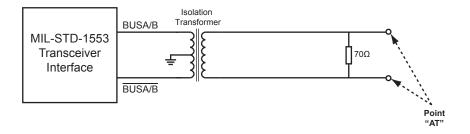

| Threshold Voltage                          | Detect                    | V <sub>THD</sub>  | 1 MHz Sine Wave (Measured                        | 0.86   | -   | 14.0 | Vp-p            |

| (Transformer-Coupled)                      | No Detect                 | V <sub>THND</sub> | at Point "AT" in Figure 8)                       | -      | -   | 0.2  | Vp-p            |

| TRANSMITTER (Measured at Po                | int "AD" in Figure 7 unle | ess otherwis      | se specified)                                    |        |     |      |                 |

|                                            | Direct Coupled            | V <sub>out</sub>  | 35Ω Load                                         | 6.6    | -   | 9.0  | Vp-p            |

| Output Voltage                             | Transformer Coupled       | V <sub>OUT</sub>  | 70Ω Load (Measured at Point<br>"AT" in Figure 8) | 20.0   | -   | 27.0 | Vp-p            |

| Output Noise                               |                           | V <sub>on</sub>   | Differential, inhibited                          | -      | -   | 10.0 | mVp-p           |

|                                            | Direct Coupled            | V <sub>DYN</sub>  | 35Ω Load                                         | -90    | -   | 90   | mV              |

| Output Dynamic Offset Voltage              | Transformer Coupled       | V <sub>DYN</sub>  | 70Ω Load (Measured at Point<br>"AT" in Figure 8) | -250   | -   | 250  | mV              |

| Output Resistance                          |                           | R <sub>out</sub>  | Differential, not transmitting                   | 10     | -   | _    | kΩ              |

| Output Capacitance                         |                           | Соит              | 1 MHz sine wave                                  | -      | -   | 15   | pF              |

**Note 1:** In actual use, the highest practical transmit duty cycle is 96%, occurring when a Remote Terminal responds to a series of 32 data word transmit commands (RT to BC) repeating with minimum intermessage gap of  $4\mu s$  ( $2\mu s$  dead time) and typical RT response delay of  $5\mu s$ .

**Note 2:** While one bus continuously transmits, the power delivered by the 3.3V power supply is  $3.3V \times 720$ mA typical = 2.4W. Of this, 850mW is dissipated in the device, the remainder in the load.

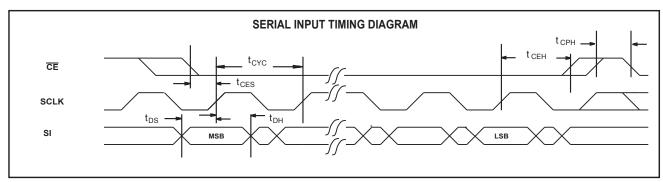

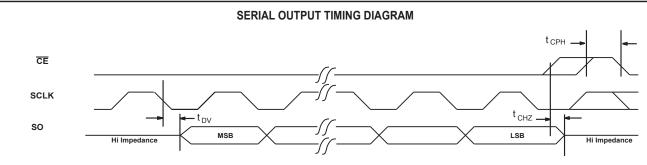

# AC Electrical Characteristics — SPI Host Interface Timing

$\rm V_{DD}$  = 3.3V, GND = 0V,  $\rm T_A$  = Operating Temperature Range (unless otherwise stated)

| Powerstern                                        |                  | Limits |     |     |       |

|---------------------------------------------------|------------------|--------|-----|-----|-------|

| Parameters                                        | Symbol           | Min    | Тур | Max | Units |

| HI-6131 INTERFACE TIMING (SPI Host Bus Interface) |                  |        |     |     |       |

| SCK clock Period                                  | t <sub>cyc</sub> | 50     | -   | -   | ns    |

| CE set-up time to first SCK rising edge           | t <sub>ces</sub> | 25     | -   | -   | ns    |

| CE hold time after last SCK rising edge           | t <sub>ceh</sub> | 25     | -   | -   | ns    |

| CE inactive between SPI instructions              | t <sub>cph</sub> | 100    | -   | -   | ns    |

| SPI SI Data set-up time to SCK rising edge        | t <sub>DS</sub>  | 10     | -   | -   | ns    |

| SPI SI Data hold time after SCK rising edge       | t <sub>DH</sub>  | 10     | -   | -   | ns    |

| SO valid after SCK falling edge                   | t <sub>DV</sub>  | -      | -   | 20  | ns    |

| SO high-impedance after CE inactive               | t <sub>cHZ</sub> | -      | -   | 75  | ns    |

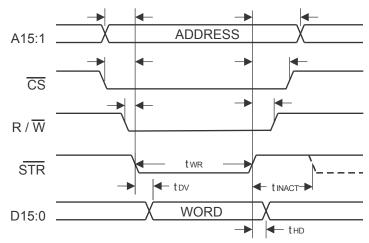

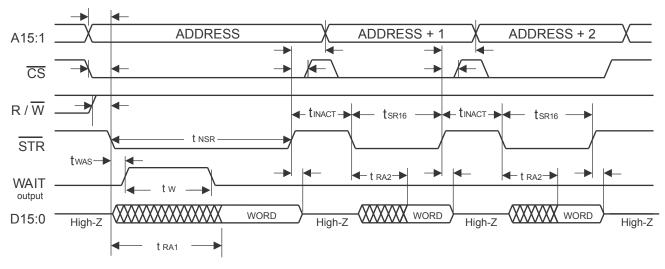

Figure 1. HI-2130 Host Bus Interface Timing Diagram

# AC Electrical Characteristics — 16-Bit Parallel Bus Host Interface Timing

|                                                                                                           |                    | Limits |     |     |       |

|-----------------------------------------------------------------------------------------------------------|--------------------|--------|-----|-----|-------|

| Parameters                                                                                                | Symbol             | Min    | Тур | Max | Units |

| WRITE TIMING                                                                                              |                    |        |     |     |       |

| Write strobe                                                                                              | t <sub>wR</sub>    | 55     | -   | -   | ns    |

| Write inactive time                                                                                       | t <sub>INACT</sub> | 25     | -   | -   | ns    |

| Write data available                                                                                      | t <sub>DV</sub>    | -      | -   | 20  | ns    |

| Write cycle, $t_{WR}$ + $t_{INACT}$                                                                       | -                  | 80     | -   | -   | ns    |

| READ TIMING                                                                                               |                    |        |     |     |       |

| Wait assertion time                                                                                       | t <sub>was</sub>   | -      | -   | 20  | ns    |

| Wait time                                                                                                 | t <sub>w</sub>     | -      | -   | 110 | ns    |

| Read strobe, sequential address, 8-bit bus mode                                                           | t <sub>SR8</sub>   | 55     | -   | -   | ns    |

| Read strobe, sequential address, 16-bit bus mode                                                          | t <sub>SR16</sub>  | 55     | -   | -   | ns    |

| Read strobe, non-sequential address                                                                       | t <sub>NSR</sub>   | 130    | -   | -   | ns    |

| Read inactive time                                                                                        | t <sub>INACT</sub> | 25     | -   | -   | ns    |

| Read access time1                                                                                         | t <sub>RA1</sub>   | -      | -   | 130 | ns    |

| Read access time2                                                                                         | t <sub>RA2</sub>   | -      | -   | 55  | ns    |

| Read cycles in 8-bit bus mode (see note below)                                                            |                    |        |     |     |       |

| Read cycle, sequential address, 16-bit word, 8-bit bus mode, $t_{SR8} + t_{INACT} + t_{SR8} + t_{INACT}$  | -                  | 160    | -   | -   | ns    |

| Read cycle, non-sequential address, 8-bit bus mode, $t_{was}$ + $t_{w}$ + $t_{inact}$ + $t_{sra}$         | -                  | -      | -   | 210 | ns    |

| Read cycles in 16-bit bus mode (see note below)                                                           |                    |        |     |     |       |

| Read cycle, sequential address, 16-bit bus mode, $\mathbf{t}_{\text{SR16}}$ + $\mathbf{t}_{\text{INACT}}$ | -                  | 80     | -   | -   | ns    |

| Read cycle, non-sequential address, 16-bit bus mode, $\mathbf{t}_{\text{WAS}}$ + $\mathbf{t}_{\text{W}}$  | -                  | -      | -   | 130 | ns    |

**NOTE:** When reading a series of sequential addresses, the read cycle for the first word (or byte) location is always longer because the HI-6130 asserts the WAIT output. As long as sequential addresses are then read, automatic prefetch speeds up read access for following words (or bytes) since these occur without WAIT assertion.

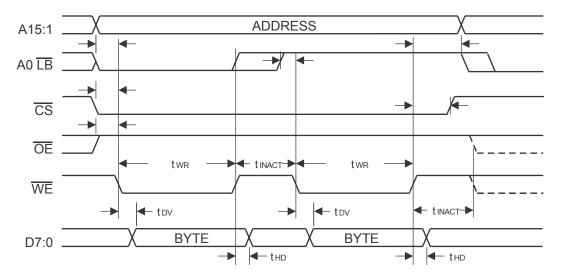

HOST WRITE IN DUAL-BYTE MODE (8-BIT BUS WIDTH) using BTYPE = 1 ("Intel Style" -  $\overline{\text{OE}}$  Output Enable and  $\overline{\text{WE}}$  Write Enable) showing 2 bytes written for a single 16-bit word

All timing intervals equal 0 ns MIN unless otherwise indicated.

The WAIT output is inactive during write access

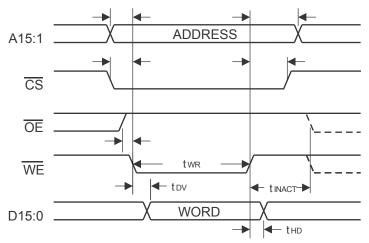

HOST WRITE IN WORD MODE (16-BIT BUS WIDTH)

using BTYPE = 1 ("Intel Style" - OE Output Enable and WE Write Enable)

showing a one-word write cycle. Successive writes to sequential addresses have same timing.

All timing intervals equal 0 ns MIN unless otherwise indicated.

The WAIT output is inactive during write access

Figure 2. Register and RAM Write Operations for BTYPE = 1

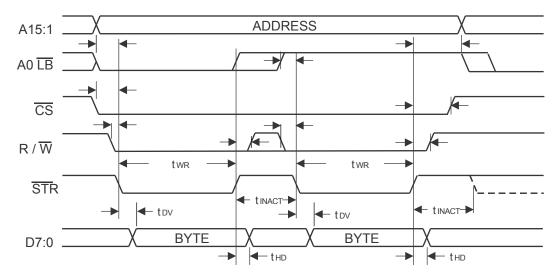

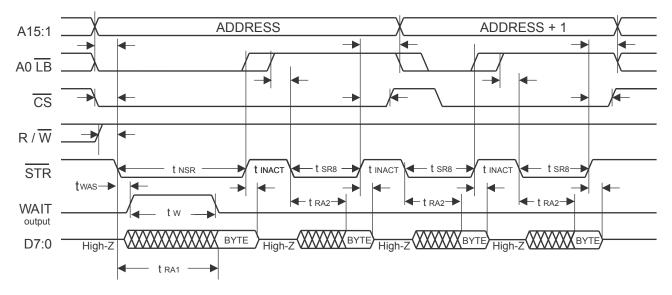

#### HOST WRITE IN DUAL-BYTE MODE (8-BIT BUS WIDTH)

using BTYPE = 0 ("Motorola Style" - Single Read/Write Strobe  $\overline{\text{STR}}$  and R/ $\overline{\text{W}}$  Direction Select) showing 2 bytes written for a single 16-bit word

All timing intervals equal 0 ns MIN unless otherwise indicated.

The WAIT output is inactive during write access

#### HOST WRITE IN WORD MODE (16-BIT BUS WIDTH)

using BTYPE = 0 ("Motorola Style" - Single Read/Write Strobe  $\overline{\text{STR}}$  and R/ $\overline{\text{W}}$  Direction Select) showing a one-word write cycle. Successive writes to sequential addresses have same timing.

All timing intervals equal 0 ns MIN unless otherwise indicated.

The WAIT output is inactive during write access

Figure 3. Register and RAM Write Operations for BTYPE = 0

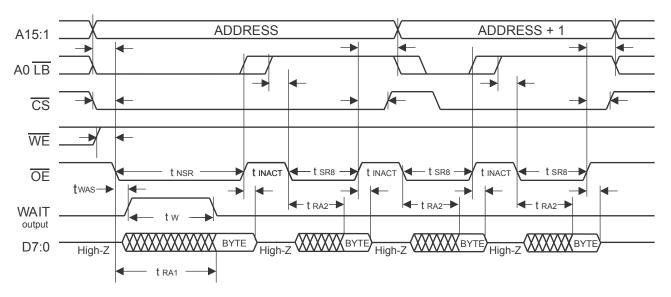

#### HOST READ IN DUAL-BYTE MODE (8-BIT BUS WIDTH)

using BTYPE = 1 ("Intel Style" -  $\overline{\text{OE}}$  Output Enable and  $\overline{\text{WE}}$  Write Enable) showing two successive 16-bit words (4 bytes) read from sequential addresses

All timing intervals equal 0 ns MIN unless otherwise indicated.

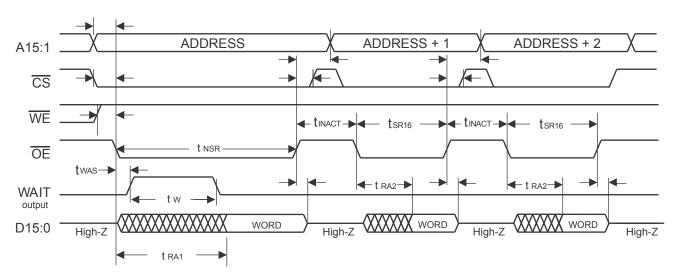

#### HOST READ IN WORD MODE (16-BIT BUS WIDTH)

using BTYPE = 1 ("Intel Style" -  $\overline{\text{OE}}$  Output Enable and  $\overline{\text{WE}}$  Write Enable) showing a three word read access from sequential addresses

All timing intervals equal 0 ns MIN unless otherwise indicated.

After first byte or word is read, prefetch allows faster access times for successive reads, as long as read addresses are sequential.

Figure 4. Register and RAM Read Operations for BTYPE = 1

#### HOST READ IN DUAL-BYTE MODE (8-BIT BUS WIDTH)

using BTYPE = 0 ("Motorola Style" - Single Read/Write Strobe STR and R/W Direction Select) showing two successive 16-bit words (4 bytes) read from sequential addresses

All timing intervals equal 0 ns MIN unless otherwise indicated.

#### HOST READ IN WORD MODE (16-BIT BUS WIDTH)

using BTYPE = 0 ("Motorola Style" - Single Read/Write Strobe STR and R/W Direction Select)

showing a three word read access from sequential addresses

All timing intervals equal 0 ns MIN unless otherwise indicated.

After first byte or word is read, prefetch allows faster access times for successive reads, as long as read addresses are sequential.

Figure 5. Register and RAM Read Operations for BTYPE = 0

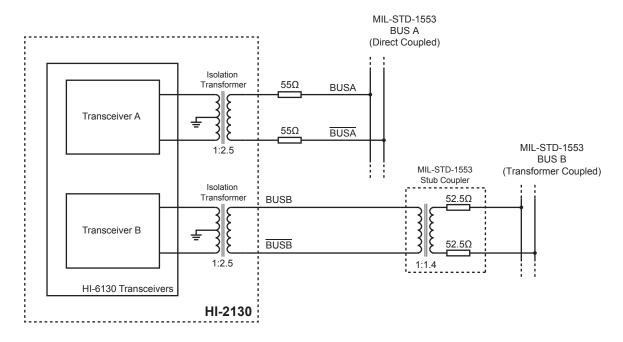

# **MIL-STD-1553 BUS INTERFACE**

Figure 6. Bus Connection Example using HI-2130

#### **Each Bus**

Figure 7. MIL-STD-1553 Direct Coupled Test Circuit Example

#### **Each Bus**

Figure 8. MIL-STD-1553 Transformer Coupled Test Circuit Example

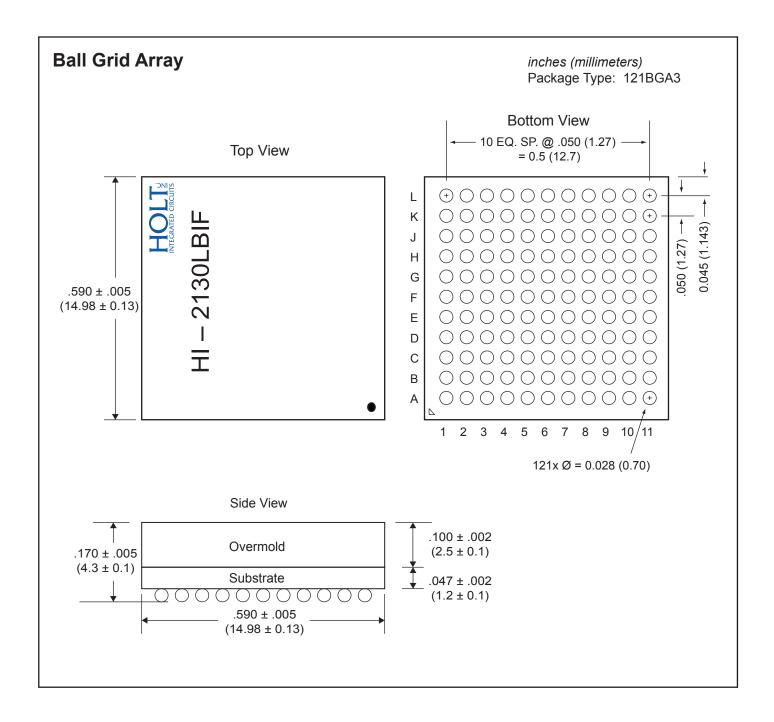

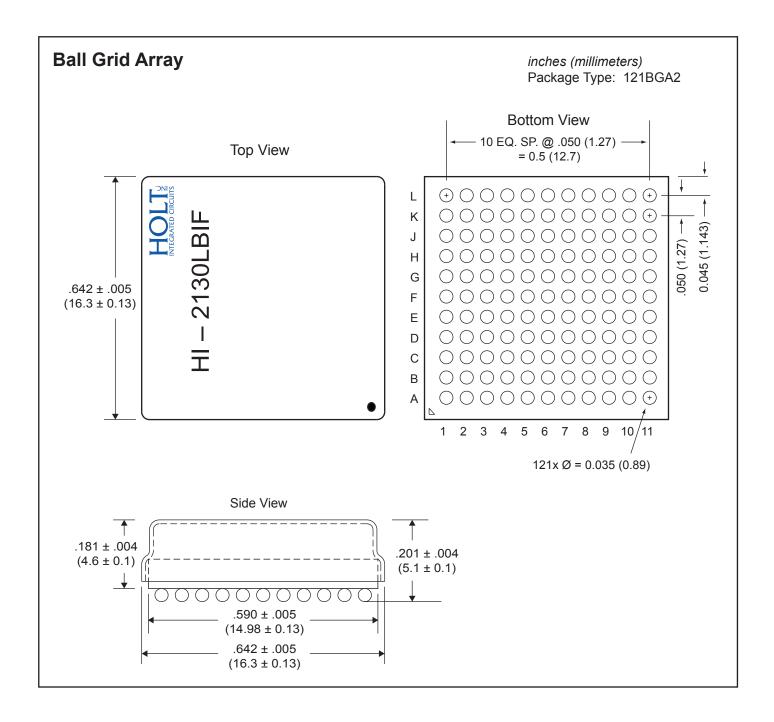

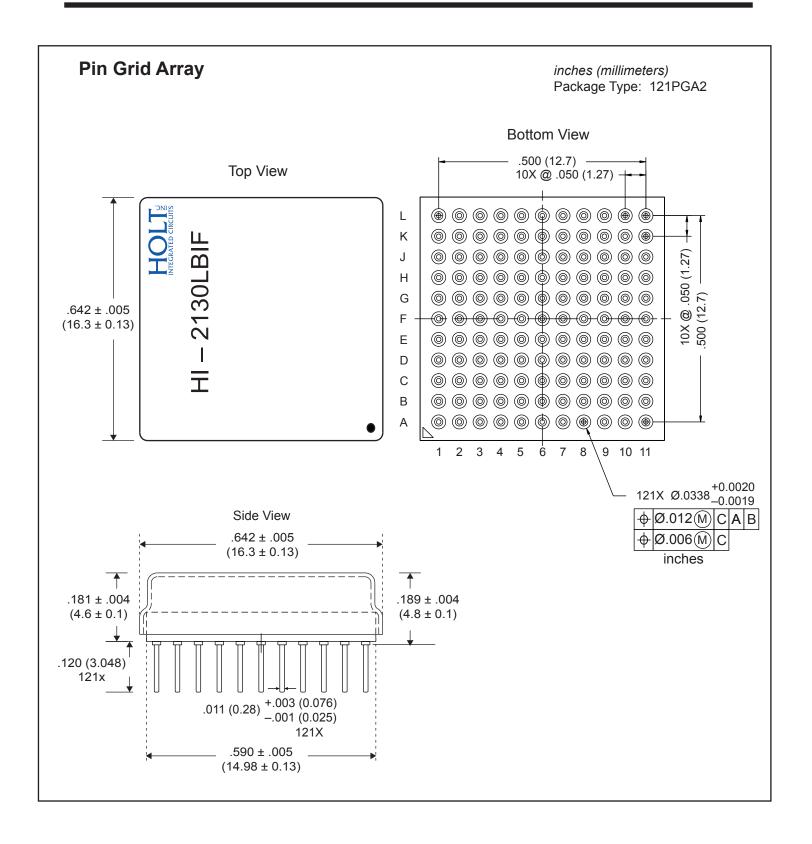

#### **PACKAGE DIMENSIONS**

# **ORDERING INFORMATION**

# HI - 2130 <u>LB x x</u>

# Lowest profile (4.4 mm), Overmold Option

| PART NUMBER | LEAD FINISH                                                     |

|-------------|-----------------------------------------------------------------|

| Blank       | Leaded Balls (Sn63Pb37)                                         |

| F           | Pb-free, RoHS compliant, SAC305 Solder Balls (Sn96.5/Ag3/Cu0.5) |

| PART NUMBER | TEMPERATURE RANGE | FLOW | BURN IN |

|-------------|-------------------|------|---------|

| 1           | -40°C to +85°C    | 1    | No      |

| Т           | -55°C to +125°C   | Т    | No      |

| PART NUMBER | PACKAGE DESCRIPTION                 |

|-------------|-------------------------------------|

| LB          | 121 BALL GRID ARRAY - BGA (121BGA3) |

# HI - 2130 <u>Gx x F</u>

# Hermetic, Metal Lid Option

| PART NUMBER | LEAD FINISH                                                     |

|-------------|-----------------------------------------------------------------|

| F           | Pb-free, RoHS compliant, SAC305 Solder Balls (Sn96.5/Ag3/Cu0.5) |

|                   | PART NUMBER | TEMPERATURE RANGE | FLOW | BURN IN |

|-------------------|-------------|-------------------|------|---------|

| $\left\{ \right.$ | 1           | -40°C to +85°C    | 1    | No      |

| Ī                 | Т           | -55°C to +125°C   | Т    | No      |

| ſ                 | M¹          | -55°C to +125°C   | М    | Yes     |

Note 1: M-Grade available for GB package option only

| _ | PART NUMBER | PACKAGE DESCRIPTION                                              |  |

|---|-------------|------------------------------------------------------------------|--|

|   | GP          | 121 PIN GRID ARRAY - PGA (121PGA2), (Pb-free, RoHS compliant)    |  |

|   | GB          | 121 BALL GRID ARRAY - BGA (121BGA2), non-collapsing solder balls |  |

# **REVISION HISTORY**

| Re          | evision | Date     | Description of Change                                                                                                                                                    |

|-------------|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DS2130, Rev | v. New  | 09/14/12 | Initial Release.                                                                                                                                                         |

| Rev         | v. A    | 11/14/12 | Corrected typos in pin diagram. Updated package drawings for new thickness. Updated Ordering Information table.                                                          |

| Rev         | v. B    | 01/22/13 | Remove LGA package option.                                                                                                                                               |

| Rev         | v. C    | 07/28/14 | Remove leaded BGA option.                                                                                                                                                |

| Rev         | v. D    | 03/18/15 | Replace "CB" and "CP" package options with low profile "GB" and "GP" package options.                                                                                    |

| Rev         | v. E    | 05/28/15 | Remove dimensions from front page package drawing.                                                                                                                       |

| Rev         | v. F    | 11/18/15 | Correct typo for OE pin.                                                                                                                                                 |

| Rev         | v. G    | 05/17/16 | Update BGA and PGA package dimensions. Total BGA package height is reduced to $5.1 \pm 0.1$ mm.                                                                          |

| Rev         | v. H    | 10/24/16 | Add new lower profile BGA package (LB).                                                                                                                                  |

| Rev         | v. J    | 11/02/17 | Add Electrical Characteristics Table.                                                                                                                                    |

| Rev         | v. K    | 07/02/18 | Update "AC Electrical Characteristics — 16-Bit Parallel Bus Host Interface Timing" parameter table and 8-bit bus width read examples to reflect two 16-bit word reads.   |

|             | v. 13   |          | Update Test Circuit Examples, Figure 7 and Figure 8.                                                                                                                     |

|             |         |          | Update ball metallurgy in "Ordering Information".                                                                                                                        |

|             |         | 03/19/19 | Correct Figure reference typos in "DC Electrical Characteristics" table.                                                                                                 |

| Rev         | v. L    |          | Update timing diagrams in Figure 2, Figure 3, Figure 4 and Figure 5. Waveforms shown incorrectly. Timing values in AC Electrical Characteristics did not change.         |

|             |         |          | Add additional timing parameters $t_{\text{DV}}$ , $T_{\text{RA1}}$ and $T_{\text{RA2}}$ to "AC Electrical Characteristics — 16-Bit Parallel Bus Host Interface Timing". |

|             |         |          | Add "M-Grade" burn-in option to "GB" package.                                                                                                                            |

| Rev         | v. M    | 07/31/19 | Change maximum reflow temperature from 260°C to 245°C in "Absolute Maximum Ratings".                                                                                     |

| Rev         | v. N    | 01/10/20 | Show position of "dot" for pin A1 on top of package.                                                                                                                     |