## HI-6230

Fully Integrated MIL-STD-1553 BC/RT/MT

HI-6230, HI-6231, HI-6232 Families

December 2019

#### 1. Overview

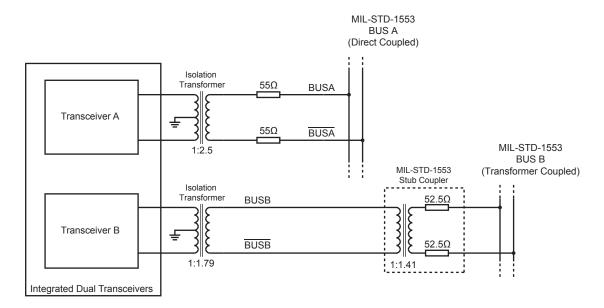

The HI-6230/31/32 family is a fully integrated and dual redundant MIL-STD-1553 BC/RT/MT interface solution which includes 1553 protocol, SRAM and dual transceivers in single plastic BGA and ceramic package configurations. The devices are direct pin compatible drop-in replacements for the Data Device Corporation (DDC®) Enhanced Mini-ACE® and Micro-ACE® Families of MIL-STD-1553 Terminals.

#### 1.1. Bus Controller

The BC is a programmable message-sequencing engine programmed using a set of 20 instruction op codes. It greatly reduces the host's processing workload by autonomously supporting multi-frame message scheduling, message retry schemes, storage of message data in on-chip RAM, asynchronous message insertion and status/error reporting. The Enhanced BC mode also includes a General Purpose Queue and user-defined interrupts to further enhance host communication.

#### 1.2. Remote Terminal

The RT has been fully validated by a recognized independent third party. RT memory management options include single, double, and 2 circular buffer modes for individual subaddresses. The RT performs comprehensive error checking including word and format validation and checks for various transfer errors. The RT supports flexible interrupt conditions, command illegalization and a programmable busy bit by subaddress.

#### 1.3. Monitor Terminal

The family supports three monitor modes including a word monitor mode, a selective message monitor mode and a combined RT/Monitor Mode. For new applications it is recommended to implement the selective message monitor mode. Selective Message Monitor allows monitoring of 1553 messages and provides the ability to filter based on RT address,  $T/\overline{R}$  bit and subaddress with no host processor intervention.

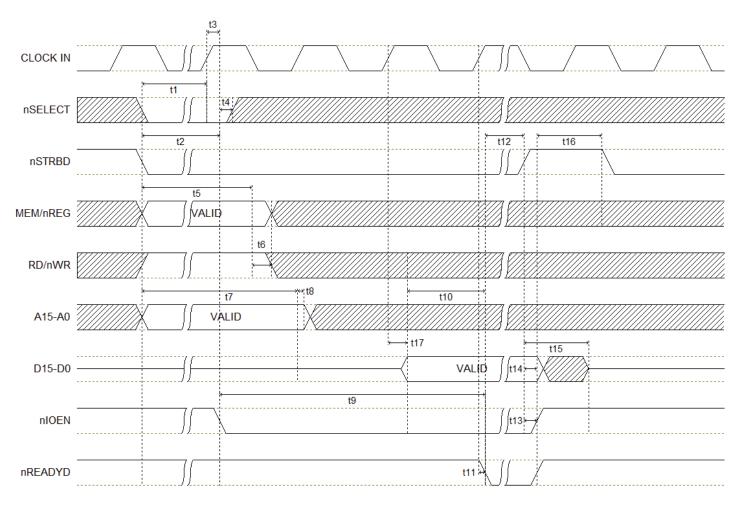

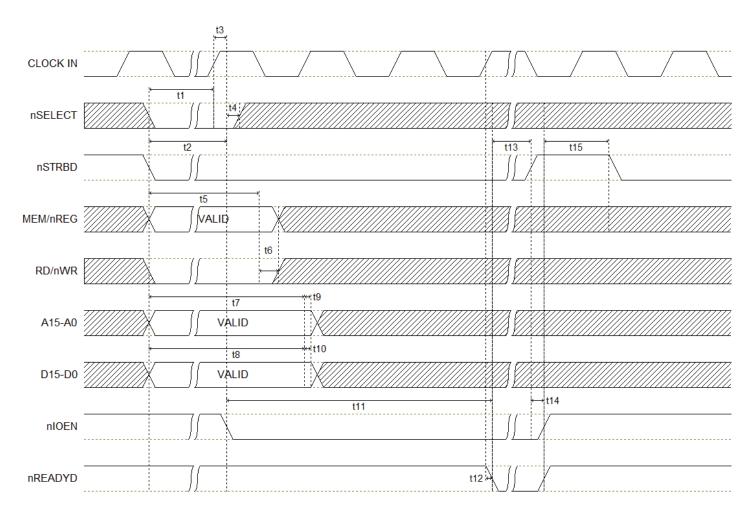

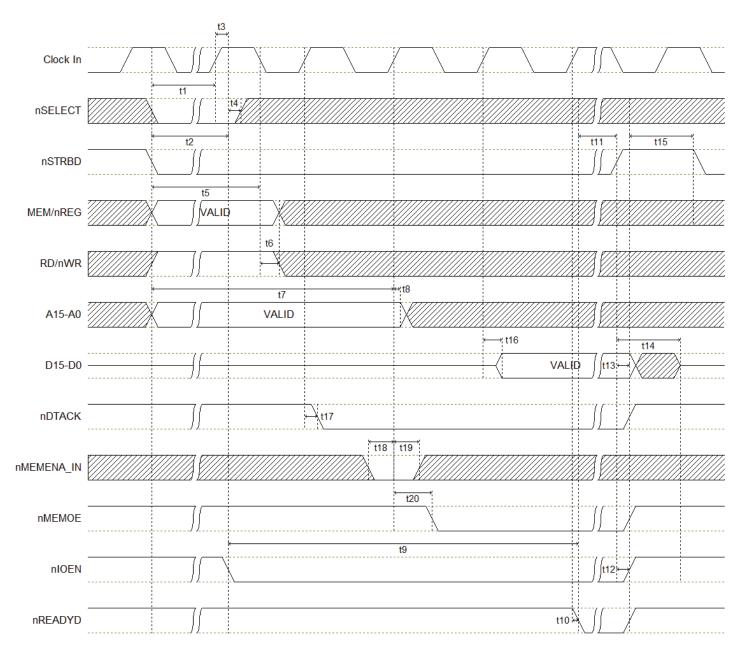

#### 1.4. Host Processor Interface

Each device provides an 8/16-bit parallel host bus interface supporting a variety of processor configurations including shared RAM and DMA configurations. The host interface supports both non-multiplexed and multiplexed address/data buses, non-zero wait mode for interfacing to processor address/data buses, and zero wait mode for interfacing to microcontroller I/O ports.

#### 1.5. Built in Test

The family provides an autonomous built-in self-test capability. The testing includes both RAM and protocol logic tests which may be initiated by the host processor.

Note: DDC®, Mini-ACE®, Enhanced Mini-ACE®, Micro-ACE®, Mini-ACE® Mark3 and Total-ACE® are registered trademarks of Data Device Corporation, Bohemia, NY, USA. There is no affiliation between Data Device Corporation and Holt Integrated Circuits Inc.

#### Overview

#### 1.6. Features

- Dual Redundant MIL-STD-1553A/B/1760 Channel

- BC, RT, MT, or RT/MT Modes

- RT only configuration available

- 64Kx17 or 4Kx16 SRAM

- 64Kx17 RAM Devices Have Built-In Parity Check

- External RT Address Inputs

- Select Products Support McAir Protocol

- Built-in Self-Test

- Generic 8/16-bit Processor Interface

- -40°C to +85°C or -55°C to +125°C

- No Limitations on transmit duty cycle

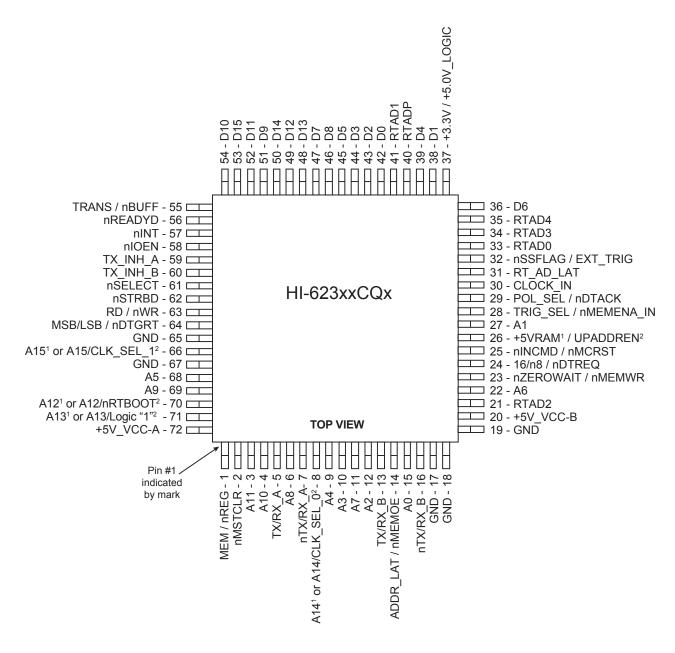

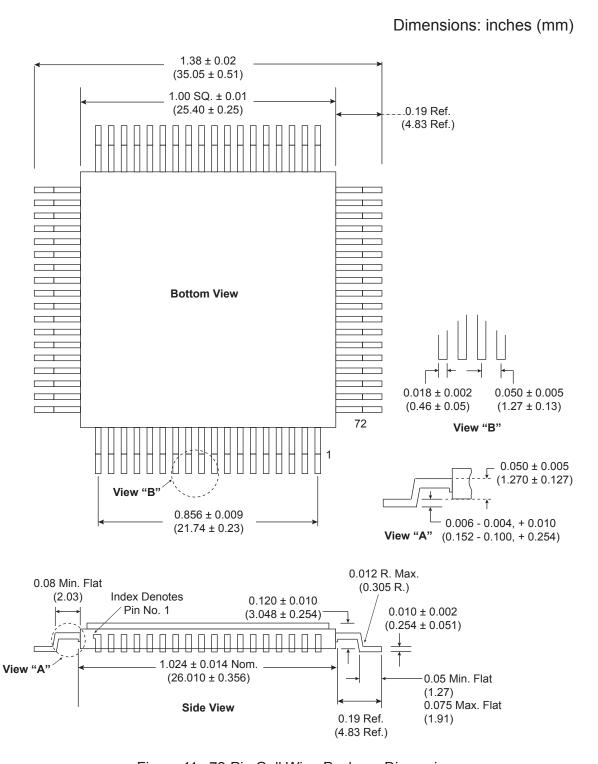

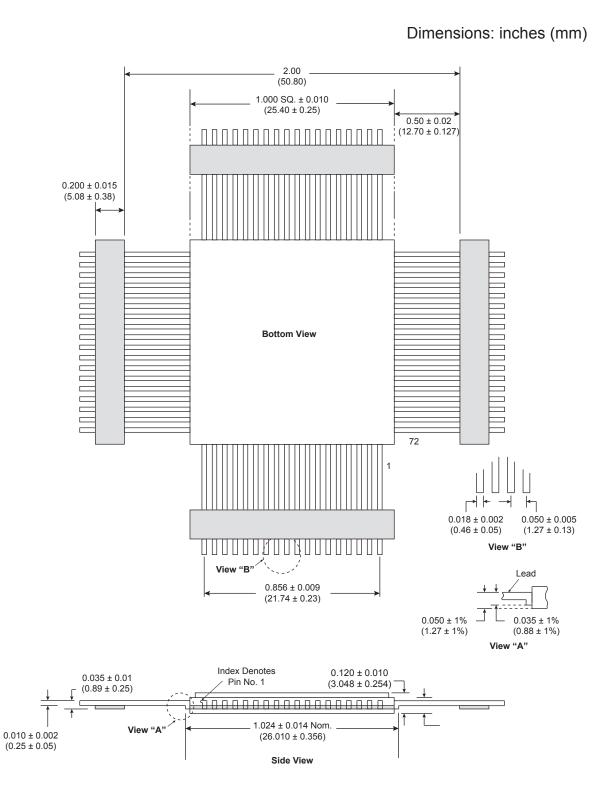

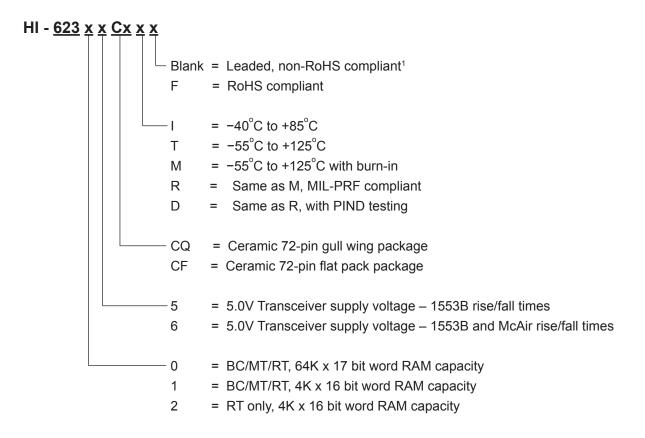

- 72-Pin Hermetic Gull Wing or Flat Pack Packages (HI-623x5CQxF and HI-623x5CFxF devices)

- o 25.4mm x 25.4mm x 3.6mm

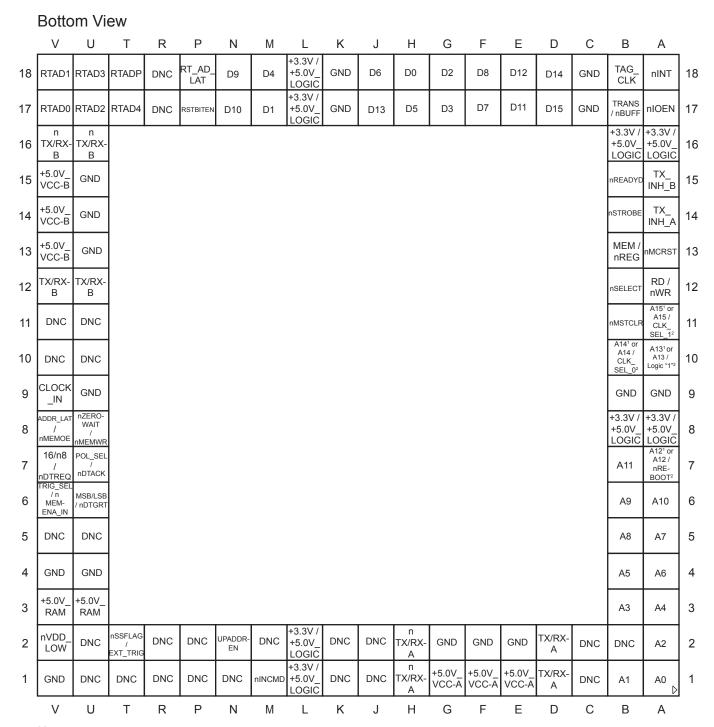

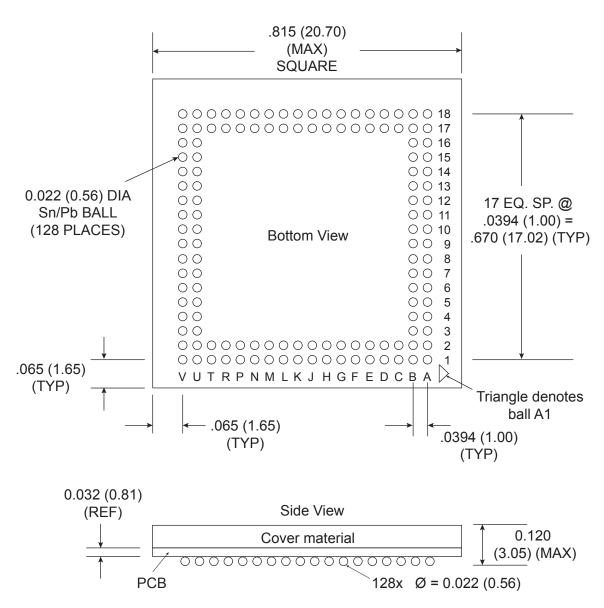

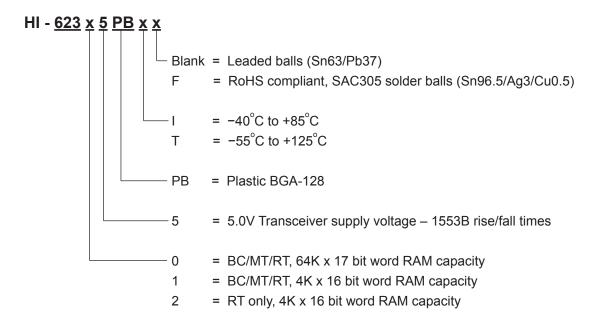

- PBGA-128 (HI-623x5PBx devices)

- o 20.7mm x 20.7mm x 3.1mm

#### 1.7. Application Benefits

- · Simplified Board Design and Layout

- Third Party RT Validated

- Single Die for Improved Reliability

- Cost Effective Direct Drop-in Replacement for DDC® Enhanced Mini-ACE® and Micro-ACE® families

- Fully Software Compatible to DDC<sup>®</sup> ACE, Mini-ACE<sup>®</sup>, Enhanced Mini-ACE<sup>®</sup>, Micro-ACE<sup>®</sup>, Mini-ACE<sup>®</sup> Mark3 and Total-ACE<sup>®</sup>.

### 1.8. Cross Reference Guide

| Holt P/N      | DDC® P/N       |

|---------------|----------------|

| HI-62325CQxF  | BU-61743G3-xxx |

| HI-02323CQXF  | BU-61745G3-xxx |

| HI-62325CFxF  | BU-61743F3-xxx |

| HI-02323CFXF  | BU-61745F3-xxx |

| HI-62326CQxF  | BU-61743G4-xxx |

| HI-62315CQxF  | BU-61843G3-xxx |

| HI-023 13CQXF | BU-61845G3-xxx |

| HI-62315CFxF  | BU-61843F3-xxx |

| HI-02313CFXF  | BU-61845F3-xxx |

| HI-62316CFxF  | BU-61843F4-xxx |

| HI-62305CQxF  | BU-61864G3-xxx |

| 111-02303CQXF | BU-61865G3-xxx |

| HI-62305CFxF  | BU-61864F3-xxx |

| TII-02303CFXF | BU-61865F3-xxx |

| HI-62306CQxF  | BU-61864G4-xxx |

| HI-62306CFxF  | BU-61864F4-xxx |

| HI-62305PBxF  | BU-61860R3-xxx |

| HI-62305PBx   | BU-61860B3-xxx |

| HI-62315PBxF  | BU-61840R3-xxx |

| HI-62315PBx   | BU-61840B3-xxx |

| HI-62325PBxF  | BU-61740R3-xxx |

| HI-62325PBx   | BU-61740B3-xxx |

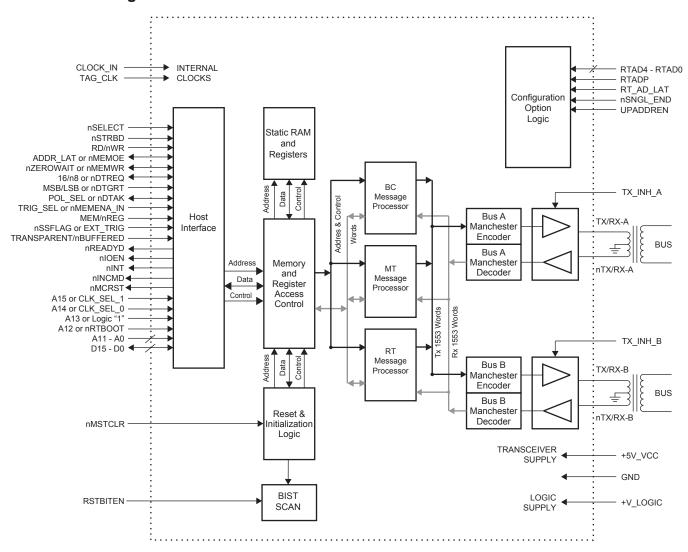

#### 1.9. Block Diagram

Table 1 summarizes the device registers and corresponding addresses.

Table 1. Register Summary

| Hex<br>Address | Access | Register Name                                                                                                   | Hard<br>Reset<br>Default |  |  |

|----------------|--------|-----------------------------------------------------------------------------------------------------------------|--------------------------|--|--|

| 0x0000         | RD/WR  | Interrupt Enable Register 1                                                                                     | 0x0000                   |  |  |

| 0x0001         | RD/WR  | Configuration Register 1                                                                                        | 0x0000                   |  |  |

| 0x0002         | RD/WR  | Configuration Register 2                                                                                        | 0x0000                   |  |  |

| 0x0003         | WR     | Start/Reset Register                                                                                            | 0x0000                   |  |  |

| 0x0003         | RD     | Non-Enhanced BC or RT Command Stack Pointer / Enhanced BC Instruction List Pointer Register                     | 0x0000                   |  |  |

| 0x0004         | RD/WR  | BC Control Word / RT Subaddress Control Word Register                                                           | 0x0000                   |  |  |

| 0x0005         | RD/WR  | Time Tag Register                                                                                               | 0x0000                   |  |  |

| 0x0006         | RD     | Interrupt Status Register 1                                                                                     | 0x0000                   |  |  |

| 0x0007         | RD/WR  | Configuration Register 3                                                                                        | 0x0000                   |  |  |

| 0x0008         | RD/WR  | Configuration Register 4                                                                                        | 0x0000                   |  |  |

| 0x0009         | RD/WR  | Configuration Register 5                                                                                        | Note 1                   |  |  |

| 0x000A         | RD/WR  | RT/Monitor Data Stack Address Register                                                                          | 0x0000                   |  |  |

| 0x000B         | RD     | BC Frame Time Remaining Register                                                                                | 0x0000                   |  |  |

| 0x000C         | RD     | BC Time Remaining to Next Message Register                                                                      | 0x0000                   |  |  |

| 0x000D         | RD/WR  | Non-Enhanced BC Frame Time / Enhanced BC Initial Instruction Pointer / RT Last Command/MT Trigger Word Register | 0x0000                   |  |  |

| 0x000E         | RD     | RT Status Word Register                                                                                         | 0x0000                   |  |  |

| 0x000F         | RD     | RT BIT Word Register                                                                                            | 0x0000                   |  |  |

| 0x0010         | -      | Test Mode Register 0                                                                                            | 0x0000                   |  |  |

| 0x0011         | _      | Test Mode Register 1                                                                                            | 0x0000                   |  |  |

| 0x0012         | -      | Test Mode Register 2                                                                                            | 0x0000                   |  |  |

| 0x0013         | _      | Test Mode Register 3                                                                                            |                          |  |  |

| 0x0014         | -      | Test Mode Register 4                                                                                            |                          |  |  |

| 0x0015         | -      | Test Mode Register 5                                                                                            | 0x0000                   |  |  |

| 0x0016         | _      | Test Mode Register 6                                                                                            | 0x0000                   |  |  |

| Hex<br>Address | Access | Register Name                                                                    | Hard<br>Reset<br>Default |  |  |

|----------------|--------|----------------------------------------------------------------------------------|--------------------------|--|--|

| 0x0017         | -      | Test Mode Register 7                                                             | 0x0000                   |  |  |

| 0x0018         | RD/WR  | Configuration Register 6                                                         | 0x0000                   |  |  |

| 0x0019         | RD/WR  | Configuration Register 7                                                         | 0x0000                   |  |  |

| 0x001A         | -      | Reserved                                                                         | 0x0000                   |  |  |

| 0x001B         | RD     | BC Condition Code Register                                                       | 0x0000                   |  |  |

| 0x001B         | WR     | BC General Purpose Flag Register                                                 |                          |  |  |

| 0x001C         | RD     | BIT Test Status Register                                                         |                          |  |  |

| 0x001D         | RD/WR  | Interrupt Enable Register 2                                                      |                          |  |  |

| 0x001E         | RD     | Interrupt Status Register 2                                                      | Note 2                   |  |  |

| 0x001F         | RD/WR  | BC General Purpose Queue Pointer / RT-MT Interrupt Status Queue Pointer Register | 0x0000                   |  |  |

#### **NOTES:**

- 1. Bits SNGLEND, TXINHA, TXINHB, RTAD[4:0] and RTADP will reflect the logic values of their respective input pins.

- 2. Following Built-in Self Test, registers 0x001C (BIT Test Status Register) and 0x001E (Interrupt Status Register 2) will be non-zero. The value of register 0x001C will depend on the result of the Built-in Self Test. In register 0x001E, bit 2, BIST, will be set to logic "1" following Built-in Self Test.

### 2.1. Interrupt Enable Register #1, Read/Write 0x0000

Setting a respective bit below to logic "1" will cause an interrupt to be generated when the corresponding event occurs. The equivalent bit in Interrupt Status Register #1 will also be set to logic "1" regardless of whether the enable bit is set or not. Setting a respective bit below to logic "0" will disable (mask) the interrupt.

| Bit No.  | Mnemonic | R/W | Reset | Bit Description                                                                                                                                                                                             |

|----------|----------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 (MSB) |          | -   | 0     | Reserved                                                                                                                                                                                                    |

| 14       | RAMPE    | R/W | 0     | Set RAMPE to logic "1" to generate an interrupt when a RAM parity error occurs.  Note: RAM PARITY ERROR must be set to logic "0" for 4K RAM device options, since there is no 17-bit RAM for these devices. |

| 13       | ТХТО     | R/W | 0     | Set TXTO to logic "1" to generate an interrupt when a transmitter timeout occurs.                                                                                                                           |

| 12       | STKRO    | R/W | 0     | Set STKRO to logic "1" to generate an interrupt when a command stack rollover occurs. When in BC Mode, this applies to the BC Command Stack. When in RT Mode, this applies to the RT Command Stack.         |

| 11       | MTRO     | R/W | 0     | Set MTRO to logic "1" to generate an interrupt when an MT command stack rollover occurs.                                                                                                                    |

| 10       | MTDRO    | R/W | 0     | Set MTDRO to logic "1" to generate an interrupt when an MT data stack rollover occurs.                                                                                                                      |

| 9        | HSKF     | R/W | 0     | Set HSKF to logic "1" to generate an interrupt when a handshake failure occurs between the device and external RAM in Transparent Mode.                                                                     |

| 8        | BCRTY    | R/W | 0     | Set BCRTY to logic "1" to generate an interrupt when the BC tries to re-send a message, regardless of whether the retry was successful or not.                                                              |

| 7        | RTAPF    | R/W | 0     | Set RTAPF to logic "1" to generate an interrupt when the The Remote Terminal address and parity bits do not exhibit odd parity.                                                                             |

| 6        | TTRO     | R/W | 0     | Set TTRO to logic "1" to generate an interrupt when the time tag counter rolls over.                                                                                                                        |

| 5        | RTCIRO   | R/W | 0     | Set RTCIRO to logic "1" to generate an interrupt when the RT circular buffer rolls over                                                                                                                     |

| 4        | CWEOM    | R/W | 0     | Set CWEOM to logic "1" to generate an interrupt at the end of the current message provided the EOM interrupt is enabled in the respective BC or RT subaddress control word.                                 |

| 3        | BCEOF    | R/W | 0     | Set BCEOF to logic "1" to generate an interrupt at the end of the current BC frame                                                                                                                          |

| 2        | ERR      | R/W | 0     | Set ERR to logic "1" to generate an interrupt when a 1553 Message Error, loopback failure or response timeout is detected                                                                                   |

| Bit No. | Mnemonic | R/W | Reset | Bit Description                               |                                                                                             |

|---------|----------|-----|-------|-----------------------------------------------|---------------------------------------------------------------------------------------------|

|         |          |     |       | The function of this bit BC, RT or MT mode as | depends on whether the device is operating in s follows:                                    |

|         |          |     |       | Set BRMINT to logic "below are met:           | 1" to generate an interrupt when the conditions                                             |

| 1       | BRMINT   | R/W | 0     | BC Mode                                       | A received RT Status Word contains the wrong RT address or an unexpected status bit value.  |

|         |          |     |       | Enhanced RT Mode                              | A valid Mode Command is received.                                                           |

|         |          |     |       | Word Monitor Mode                             | A valid received command word matches the value programmed in the Monitor Trigger Register. |

| 0 (LSB) | EOM      | R/W | 0     | Set EOM to logic "1" to message.              | generate an interrupt at the end of every                                                   |

### 2.2. Configuration Register #1, Read/Write 0x0001

Configuration Register #1 is used to select the device's mode of operation and for software control of operational features such as RT Status Word bits, Time-Tagging, etc. Specific bit functionality depends on the selected mode of operation as outlined in the Tables below.

Table 2. Configuration Register #1, Non-Enhanced BC Mode (Legacy).

| Bit No.  | Mnemonic | R/W | Reset | Bit Description                                                                                                                                                                                                |

|----------|----------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 (MSB) | MODE1    | R/W | 1     | Set to logic "0" for BC mode of operation.                                                                                                                                                                     |

| 14       | MODE2    | R/W | 0     | Initializes logic "0" in BC mode.                                                                                                                                                                              |

| 13       | MEMAB    | R/W | 0     | This bit indicates which fixed memory location is used.  If MEMAB is logic "0", Location A is used  If MEMAB is logic "1", Location B is used.                                                                 |

| 12       | ABRTME   | R/W | 0     | Set ABORTME to logic "1" to abort message processing at the end of the current message when the BC encounters a message error. BC Message processing will continue if an optional message retry is successful. |

| 11 – 0   | -        | R/W | 0     | Used only in Enhanced BC Mode (see below)                                                                                                                                                                      |

Table 3. Configuration Register #1, Enhanced BC Mode.

To enable Enhanced BC Mode, bit 15 of Configuration Register #1 should be set to logic "0" **AND** bit 15 of Configuration Register #3 should be set to logic "1".

| Bit No.  | Mnemonic  | R/W    | Reset | Bit Description                                                                                                                                                                                                                                                                 |

|----------|-----------|--------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 (MSB) | MODE1     | R/W    | 1     | Set to logic "0" for BC mode of operation.                                                                                                                                                                                                                                      |

| 14       | MODE2     | R/W    | 0     | Initializes logic "0" in BC mode.                                                                                                                                                                                                                                               |

| 13       | MEMAB     | R/W    | 0     | Current Memory Pointer.                                                                                                                                                                                                                                                         |

| 13       | IVILIVIAD | IVVV   | 0     | Logic "0" for Location A, logic "1" for Location B.                                                                                                                                                                                                                             |

|          |           |        |       | Abort at End of Message if Error.                                                                                                                                                                                                                                               |

| 12       | ABRTME    | R/W    | 0     | Set to logic "1" to abort message processing at the end of the current message when the BC encounters an error. BC Message processing will continue if the message retry feature is enabled and retry is successful.                                                            |

|          |           |        |       | Abort at End of Frame if Error.                                                                                                                                                                                                                                                 |

| 11       | ABRTFE    | R/W    | 0     | Set to logic "1" to abort message processing at the end of the current frame when the BC encounters an error. BC Message processing will continue if the message retry feature is enabled and retry is successful.                                                              |

|          |           |        |       | Abort at End of Message if Status Bits Set.                                                                                                                                                                                                                                     |

| 10       | ABRTMES   | R/W    | 0     | Set to logic "1" to abort message processing at the end of the current message when non-masked Status Word bits are set unexpectedly. BC Message processing will continue if the message retry feature is enabled and retry is successful.                                      |

|          |           |        |       | Abort at End of Frame if Status Bits Set.                                                                                                                                                                                                                                       |

| 9        | ABRTFES   | R/W    | 0     | Set to logic "1" to abort message processing at the end of the current frame (even if Auto Frame Repeat is enabled) when non-masked Status Word bits are set unexpectedly. BC Message processing will continue if the message retry feature is enabled and retry is successful. |

|          |           |        |       | Auto Frame Repeat.                                                                                                                                                                                                                                                              |

|          | 8 AFR R   | D 0.4/ | •     | Logic "0": The host manually starts each BC frame.                                                                                                                                                                                                                              |

| 8        |           | R/W    | 0     | Logic "1": BC frame will repeat indefinitely provided none of the conditions outlined in bits 12:9 occur or the part is not reset. A fixed frame time may be set by setting bit 6, Internal Trigger below.                                                                      |

|          |           |        |       | External Trigger.                                                                                                                                                                                                                                                               |

| 7        | ETRIG     | R/W    | 0     | Set to logic "1" to start BC message processing via rising edge of EXT_TRIG signal.                                                                                                                                                                                             |

| Bit No. | Mnemonic | R/W | Reset | Bit Description                                                                                                                                                                                                                                       |

|---------|----------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |          |     |       | Internal Trigger.                                                                                                                                                                                                                                     |

| 6       | ITRIG    | R/W | 0     | This bit is used in conjunction with bit 8, Auto Frame Repeat, to automatically repeat the BC frame with a fixed frame time. The time is set in increments of 100µs (up to 6.55 sec.) according to the value specified by the BC Frame Time Register. |

|         |          |     |       | Logic "1": Enable.                                                                                                                                                                                                                                    |

|         |          |     |       | Logic "0": Disable. Stop after a single frame.                                                                                                                                                                                                        |

|         |          |     |       | Message Gap Timer.                                                                                                                                                                                                                                    |

|         |          |     |       | Logic "0": Default message gap (~10µs).                                                                                                                                                                                                               |

| 5       | GAPTMR   | R/W | 0     | Logic "1": The message gap is defined in steps of 1µs in the third word of the BC Message Block Descriptor (the defined value may be 10µs – 65.535 ms)                                                                                                |

|         |          |     |       | Message Retry.                                                                                                                                                                                                                                        |

| 4       | RTY      | R/W | R/W 0 | Logic "1": Enable BC message retries by setting bit 8 in the respective BC control word.                                                                                                                                                              |

|         |          |     |       | Logic "0": Disable message retries.                                                                                                                                                                                                                   |

| 3       | RTY2X    | R/W | 0     | If RTY2X is set to logic "1" and retries are enabled by setting bit 4 above, then the BC will retry again if the first attempt was unsuccessful.                                                                                                      |

|         |          |     |       | If RTY2X is set to logic "0", then retry only once.                                                                                                                                                                                                   |

|         |          |     |       | BC Enabled.                                                                                                                                                                                                                                           |

| 2       | BCEN R   | R   | R 0   | Logic "1" indicates the BC state machine is enabled, i.e. is active and processing messages.                                                                                                                                                          |

|         |          |     |       | Logic "0" indicates the BC is in Idle mode.                                                                                                                                                                                                           |

| 1       | BCFIP    | R   | 0     | This bit will read logic "1" for the start of the first message to the end of the last message in a BC frame.                                                                                                                                         |

| 0 (LSB) | BCMIP    | R   | 0     | This bit will read logic "1" for the duration of all BC messages.                                                                                                                                                                                     |

Table 4. Configuration Register #1, RT Mode (without Alternate Status Word).

**Configuration Register #3, bit 5 = logic "0".** For Enhanced RT operation, bit 15 of Configuration Register #3 should be set to logic "1".

| Bit No.  | Mnemonic   | R/W     | Reset | Bit Description                                                                                                                                      |                                                                                                                                             |                                                                                                                                                    |

|----------|------------|---------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 (MSB) | MODE1      | R/W     | 1     | Set to logic "1" for RT mode of operation.                                                                                                           |                                                                                                                                             |                                                                                                                                                    |

| 14       | MODE2      | R/W     | 0     | If bit 15 is logic "1" for RT operation, this bit should be logic "0". In this case, enable MT mode (i.e. RT/MT) by setting bit 12 of this register. |                                                                                                                                             |                                                                                                                                                    |

| 13       | MEMAB      | R/W     | 0     | Current Memory Pointer.                                                                                                                              |                                                                                                                                             |                                                                                                                                                    |

| 13       | IVICIVIAD  | IN/ V V | U     | Logic "0" for Location A, logic "1" for Location B.                                                                                                  |                                                                                                                                             |                                                                                                                                                    |

|          |            |         |       | Message Monitor Enable                                                                                                                               |                                                                                                                                             |                                                                                                                                                    |

| 12       | MTEN       | R/W     | 0     | Logic "1": Enable Message Monitor.                                                                                                                   |                                                                                                                                             |                                                                                                                                                    |

|          |            |         |       | Logic "0": Disable Message Monitor.                                                                                                                  |                                                                                                                                             |                                                                                                                                                    |

|          |            |         |       | Dynamic Bus Control Acceptance, active low.                                                                                                          |                                                                                                                                             |                                                                                                                                                    |

| 11       | DBAC       | R/W     | R/W   | R/W                                                                                                                                                  | 0                                                                                                                                           | Logic "0": The RT will respond to a Dynamic Bus Control Mode Code Command by setting the Dynamic Bus Control Acceptance bit in the RT Status Word. |

|          |            |         |       | Logic "1": The Dynamic Bus Control Acceptance bit in the RT Status Word will always be zero.                                                         |                                                                                                                                             |                                                                                                                                                    |

|          |            |         |       | Busy Bit, active low.                                                                                                                                |                                                                                                                                             |                                                                                                                                                    |

| 10       | BUSY       | R/W     | R/W   | 0                                                                                                                                                    | Logic "0" will result in "busy" status set. The RT will not respond to commands and will transmit the RT Status Word with the busy bit set. |                                                                                                                                                    |

|          |            |         |       | Logic "1" results in the busy bit not set in the RT Status Word and the RT will respond to commands in the normal way.                               |                                                                                                                                             |                                                                                                                                                    |

|          |            |         |       | Service Request Bit, active low.                                                                                                                     |                                                                                                                                             |                                                                                                                                                    |

| 9        | SVCREQ R/W | R/W     | 0     | Logic "0" will result in the Service Request bit set in the RT Status Word.                                                                          |                                                                                                                                             |                                                                                                                                                    |

|          |            |         |       | Logic "1" will result in the Service Request bit not set in the RT Status Word.                                                                      |                                                                                                                                             |                                                                                                                                                    |

|          | 8 SSYS RA  |         | w 0   | Subsystem Flag Bit, active low.                                                                                                                      |                                                                                                                                             |                                                                                                                                                    |

| 8        |            | R/W     |       | Logic "0" will result in the Subsystem Flag bit set in the RT Status Word.                                                                           |                                                                                                                                             |                                                                                                                                                    |

|          |            |         |       | Logic "1" will result in the Subsystem Flag bit not set in the RT Status Word.                                                                       |                                                                                                                                             |                                                                                                                                                    |

| Bit No. | Mnemonic      | R/W | Reset | Bit Description                                                                                   |

|---------|---------------|-----|-------|---------------------------------------------------------------------------------------------------|

|         |               |     |       | Terminal Flag Bit, active low.                                                                    |

|         |               |     |       | Enhanced Mode only (Configuration Register #3, bit 15 = logic "1").                               |

| 7       | TF            | R/W | 0     | Logic "0" will result in the Terminal Flag bit set in the RT Status Word.                         |

|         |               |     |       | Logic "1" will result in the Terminal Flag bit not set in the RT Status Word.                     |

| 6 – 1   |               | -   | -     | Not used.                                                                                         |

|         |               |     |       | RT Message in Progress.                                                                           |

| 0 (LSB) | 0 (LSB) RTMIP | R   | 0     | Enhanced Mode only (Configuration Register #3, bit 15 = logic "1").                               |

| 3 (202) |               | K   |       | Logic "1" indicates the RT is processing a message. Set just before SOM and reset just after EOM. |

Table 5. Configuration Register #1, RT Mode (with Alternate Status Word).

**Configuration Register #3, bit 5 = logic "1".** Bits 11 – 1 of the RT status word are programmable directly by the host. For use of the RT Alternate Status word, Enhanced RT operation must be activated (bit 15 of Configuration Register #3 should be set to logic "1").

| Bit No.  | Mnemonic | R/W | Reset | Bit Description                                                                               |

|----------|----------|-----|-------|-----------------------------------------------------------------------------------------------|

| 15 (MSB) | MODE1    | R/W | 1     | Set to logic "1" for RT mode of operation.                                                    |

| 14       | MODE2    | R/W | 0     | Set to logic "0" for RT mode of operation.                                                    |

| 13       | MEMAB    | R/W | 0     | Current Memory Pointer.  Logic "0" for Location A, logic "1" for Location B.                  |

| 12       | MTEN     | R/W | 0     | Message Monitor Enable Logic "1": Enable Message Monitor. Logic "0": Disable Message Monitor. |

| 11       | MERR     | R/W | 0     | If this bit is logic "1", the Message Error bit (bit 9) of the RT Status Word will be set.    |

| 10       | INS      | R/W | 0     | If this bit is logic "1", the Instrumentation bit (bit 10) of the RT Status Word will be set. |

| 9        | SVCREQ   | R/W | 0     | If this bit is logic "1", the Service Request bit (bit 11) of the RT Status Word will be set. |

| 8        | RSRV1    | R/W | 0     | If this bit is logic "1", bit 12 of the RT Status Word will be set.                           |

| 7        | RSRV2    | R/W | 0     | If this bit is logic "1", bit 13 of the RT Status Word will be set.                           |

| 6        | RSRV3    | R/W | 0     | If this bit is logic "1", bit 14 of the RT Status Word will be set.                           |

| Bit No. | Mnemonic | R/W | Reset | Bit Description                                                                                      |

|---------|----------|-----|-------|------------------------------------------------------------------------------------------------------|

| 5       | BCST     | R/W | 0     | If this bit is logic "1", Broadcast Command Received bit (bit 15) of the RT Status Word will be set. |

| 4       | BUSY     | R/W | 0     | If this bit is written logic "1", the Busy bit (bit 16) of the RT Status Word will be set.           |

| 3       | SSYS     | R/W | 0     | If this bit is written logic "1", the Subsystem Flag bit (bit 17) of the RT Status Word will be set. |

| 2       | DBAC     | R/W | 0     | If this bit is written logic "1", bit 18 of the RT Status Word will be set.                          |

| 1       | TF       | R/W | 0     | If this bit is written logic "1", the Terminal Flag bit (bit 19) of the RT Status Word will be set.  |

|         |          |     |       | RT Message in Progress.                                                                              |

| 0 (LSB) | RTMIP    | R   | 0     | Logic "1" indicates the RT is processing a message. Set just before SOM and reset just after EOM.    |

Table 6. Configuration Register #1, Enhanced Monitor Mode.

Enhanced mode is activated by setting bit 15 of Configuration Register #3 to logic "1". Bits 15 - 13 apply to both Enhanced and non-Enhanced Modes. Bits 12 - 0 only apply in Enhanced Mode.

| Bit No.  | Mnemonic | R/W | Reset | Bit Description                                                                                                                                                                                                                                                                         |  |  |  |

|----------|----------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 15 (MSB) | MODE1    | R/W | 1     | Set to logic "0" for MT mode of operation.                                                                                                                                                                                                                                              |  |  |  |

| 14       | MODE2    | R/W | 0     | Set to logic "1" for MT mode of operation.                                                                                                                                                                                                                                              |  |  |  |

| 13       | MEMAB    | R/W | 0     | Current Memory Pointer.  Logic "0" for Location A, logic "1" for Location B.                                                                                                                                                                                                            |  |  |  |

| 12       | MTEN     | R/W | 0     | Message Monitor Enable Logic "1": Enable Message Monitor. Logic "0": Disable Message Monitor.                                                                                                                                                                                           |  |  |  |

| 11       | TRIGEN   | R/W | 0     | Word Monitor Trigger Enable.  Enable with logic "1". This bit must be set in Word Monitor Mode to enable a monitor start via EXT_TRIG (bit 7 below set to logic "1") or via successful comparison between a received valid word and the word stored in the MT Trigger Resister (0x00D). |  |  |  |

| 10       | TRSTRT   | R/W | 0     | Start Word Monitor on Trigger.  Enable with logic "1". The Word Monitor will start monitoring following successful comparison between a received valid word and the word stored in the MT Trigger Resister (0x00D).                                                                     |  |  |  |

| Bit No.  | Mnemonic        | R/W | Reset                                                                                                                                     | Bit Description                                                                                                                                                                    |

|----------|-----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                 |     |                                                                                                                                           | Stop Word Monitor on Trigger.                                                                                                                                                      |

| 9        | TRSTOP          | R/W | 0                                                                                                                                         | Enable with logic "1". The Word Monitor will stop monitoring following successful comparison between a received valid word and the word stored in the MT Trigger Resister (0x00D). |

| 8        | -               | -   | -                                                                                                                                         | Not used.                                                                                                                                                                          |

|          |                 |     |                                                                                                                                           | External Trigger.                                                                                                                                                                  |

| 7        | 7 EXTTRIG R/W 0 | 0   | Set to logic "1" to start MT via rising edge of EXT_TRIG signal. Monitor trigger must also be enabled by setting bit 11 of this register. |                                                                                                                                                                                    |

| 6 - 3    | -               | -   | -                                                                                                                                         | Not used.                                                                                                                                                                          |

| 2        | MEN             | R   | 0                                                                                                                                         | Monitor Enabled.                                                                                                                                                                   |

|          | IVIEIN          | K   | U                                                                                                                                         | A logic "1" indicates the Monitor is enabled.                                                                                                                                      |

|          |                 |     |                                                                                                                                           | Monitor Triggered.                                                                                                                                                                 |

| 1        | 1 MTR R 0       |     | 0                                                                                                                                         | A logic "1" indicates the Monitor was triggered either by successful comparison with the word in the MT Trigger Resister (0x00D) or via rising edge of the EXT_TRIG signal         |

| 0 (1 SB) | MACT            | R   | 0                                                                                                                                         | Monitor Active.                                                                                                                                                                    |

| 0 (LSB)  | IVIACT          | "   | U                                                                                                                                         | A logic "1" indicates the Word Monitor was started.                                                                                                                                |

### 2.3. Configuration Register #2, Read/Write 0x0002

| Bit No.  | Mnemonic | R/W    | Reset | Bit Description                                                      |                                                                                                                                                                     |               |                                                                                        |  |  |  |  |

|----------|----------|--------|-------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------------------------------------------------------------------------|--|--|--|--|

| 15 (MSB) | EINTEN   | R/W    | 0     | Set EINTEN to logic "1" to enable Enhanced Interrupts.               |                                                                                                                                                                     |               |                                                                                        |  |  |  |  |

| 14       | RAMP     | R/W    | 0     | Set RAMP to logic "1" to enable parity checking in the internal RAM. |                                                                                                                                                                     |               |                                                                                        |  |  |  |  |

| 13       | BUSYLU   | R/W    | 0     | Set BUSYLU to logic "1" to enable the Busy Lookup Table.             |                                                                                                                                                                     |               |                                                                                        |  |  |  |  |

| 12       | DBUF     | R/W    | 0     |                                                                      | Set DBUF to logic "1" to enable Double Buffering for Rx messages (see bit 1 below).                                                                                 |               |                                                                                        |  |  |  |  |

| 11       | OVINV    | R/W    | 0     | Setting OVI overwritten.                                             |                                                                                                                                                                     | 1" will cause | e invalid circular buffer data to be                                                   |  |  |  |  |

| 10       | 256RO    | R/W    | 0     | If 256RO is                                                          | logic "0", RA                                                                                                                                                       | .M buffers w  | vill rollover after 256 words.                                                         |  |  |  |  |

|          |          |        |       | Time Tag R follows:                                                  | esolution bits                                                                                                                                                      | s. Bits 9 - 7 | set the time tag resolution as                                                         |  |  |  |  |

|          |          |        |       | Bit 9                                                                | Bit 8                                                                                                                                                               | Bit 7         | Time Tag Resolution                                                                    |  |  |  |  |

|          |          |        |       | 0                                                                    | 0                                                                                                                                                                   | 0             | 64 µs                                                                                  |  |  |  |  |

|          |          |        |       | 0                                                                    | 0                                                                                                                                                                   | 1             | 32 µs                                                                                  |  |  |  |  |

|          |          |        |       | 0                                                                    | 1                                                                                                                                                                   | 0             | 16 µs                                                                                  |  |  |  |  |

| 9 - 7    | TTRES    | R/W    | 0     | 0                                                                    | 1                                                                                                                                                                   | 1             | 8 µs                                                                                   |  |  |  |  |

|          | TINES    | I FOVV |       | 1                                                                    | 0                                                                                                                                                                   | 0             | 4 μs                                                                                   |  |  |  |  |

|          |          |        |       | 1                                                                    | 0                                                                                                                                                                   | 1             | 2 μs                                                                                   |  |  |  |  |

|          |          |        |       | 1                                                                    | 1                                                                                                                                                                   | 0             | The Time Tag is incremented by writing logic "1" to bit 4 of the Start/Reset Register. |  |  |  |  |

|          |          |        |       | 1                                                                    | 1                                                                                                                                                                   | 1             | The Time Tag is incremented by means of an external clock connected to TAG_CLK.        |  |  |  |  |

| 6        | TTSYNC   | R/W    | 0     |                                                                      |                                                                                                                                                                     |               | "1" will clear the Time Tag counter mode command is received.                          |  |  |  |  |

| 5        | SYNCDAT  | R/W    | 0     | received Sy<br>Time Tag R                                            | In RT Mode, setting this bit to logic "1" will cause the data word in a received Synchronize With Data mode command to loaded into the Time Tag Register.           |               |                                                                                        |  |  |  |  |

|          |          |        |       | Tag Registe                                                          | In BC Mode, setting this bit to logic "1" will allow the value of the Time Tag Register to be transmitted as the data word in a Synchronize With Data mode command. |               |                                                                                        |  |  |  |  |

| 4        | CLRSTAT  | R/M    | 0     | Logic "1": C<br>respectively                                         |                                                                                                                                                                     | t Status Reg  | gisters #1 or #2 when read                                                             |  |  |  |  |

| +        | OLINOTAT | R/W    | 0     |                                                                      | Logic "0": Clear both Interrupt Status Registers #1 and #2 by writing logic "1" to bit 2, Start/Reset Register 0x003.                                               |               |                                                                                        |  |  |  |  |

| Bit No. | Mnemonic | R/W | Reset | Bit Description                                                                                                                                                                                       |  |                                                                                                     |

|---------|----------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-----------------------------------------------------------------------------------------------------|

|         |          |     |       | This bit sets whether the interrupt output signal INT is a continuous level or a pulse.                                                                                                               |  |                                                                                                     |

| 3       | 3 LEVEL  | R/W | 0     | Logic "1": The INT output signal will be a level that will remain low until Interrupt Status Registers #1 and #2 are cleared.                                                                         |  |                                                                                                     |

|         |          |     |       | Logic "0": The INT output signal will be a 500ns pulse.                                                                                                                                               |  |                                                                                                     |

|         |          |     |       |                                                                                                                                                                                                       |  | Logic "0": The Service Request bit in the RT Status Word may <b>only</b> be controlled by the host. |

| 2       | SRREQ    | R/W | 0     | Logic "1": The Service Request bit in the RT Status Word may be controlled by the host, but is cleared when the RT responds to a Transmit Vector Word mode code command                               |  |                                                                                                     |

|         |          |     |       | This bit is used to set the Enhanced RT buffering mode.                                                                                                                                               |  |                                                                                                     |

| 1       | ENRTBUF  | R/W | 0     | ENRTBUF = logic "0": If bit 12 of this register is logic "1", double buffer mode will be set globally for all Rx commands. If bit 12 is logic "0", single buffer mode will be set.                    |  |                                                                                                     |

|         |          |     |       | ENRTBUF = logic "1": Each Rx subaddress can have a different buffering mode, set by the individual subaddress control word.                                                                           |  |                                                                                                     |

|         |          |     |       | Notice 2 Broadcast Data Storage.                                                                                                                                                                      |  |                                                                                                     |

| 0 (LSB) | NOTICE2  | R/W | 0     | If this bit is logic "1", the terminal stores data associated with broadcast commands separately from data associated with non-broadcast commands to meet the requirements of MIL-STD-1553B Notice 2. |  |                                                                                                     |

|         |          |     |       | If this bit is logic "0", broadcast command data is stored in the same buffer with data from nonbroadcast commands.                                                                                   |  |                                                                                                     |

### 2.4. Command Stack Pointer Register/ Enhanced BC Instruction List Register, Read Only 0x0003

When read, this register contains the current value of the Stack Pointer for RT, MT and non-enhanced BC modes. In Enhanced BC Mode, this register will contain a pointer to the BC Instruction List.

| Bit No.            | R/W | Reset | Bit Description                                   |  |

|--------------------|-----|-------|---------------------------------------------------|--|

| 15 (MSB) - 0 (LSB) | R   | 0     | Command Stack Pointer, bits[15 - 0] respectively. |  |

### 2.5. Start/Reset Register, Write Only 0x0003

When writing to this register, all reserved bits must be written logic "0".

| Bit No.       | Mnemonic | R/W | Reset | Bit Description                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|---------------|----------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 15 (MSB) - 12 |          | W   | 0     | Reserved.                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 11            | RTON     | W   | 0     | If the RT goes offline following receipt of an Initiate Self-Test mode command (RTOFF bit 4 of Configuration Register #7 set), then the RT will automatically restart following completion of the self-test. However, if the host does not run the self-test by setting bit 7 of this register, then this bit should be set in order to bring the RT back online. |  |  |  |

| 10            | CLRST    | W   | 0     | Setting CLRST to logic "1" will clear the Self-Test Register                                                                                                                                                                                                                                                                                                      |  |  |  |

| 9             | RAMST    | W   | 0     | Setting PROST to logic "1" will initiate a RAM Self-Test                                                                                                                                                                                                                                                                                                          |  |  |  |

| 8             | -        | W   | 0     | Reserved                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 7             | PROST    | W   | 0     | Setting PROST to logic "1" will initiate a Protocol Self-Test                                                                                                                                                                                                                                                                                                     |  |  |  |

| 6             | STOPMSG  | W   | 0     | In BC Mode, setting this bit will stop operation at End-of-Message.  In MT Mode, setting this bit will stop message monitoring.                                                                                                                                                                                                                                   |  |  |  |

| 5             | BCSTOPFR | W   | 0     | In BC Mode, setting this bit will stop operation at End-of-Frame.                                                                                                                                                                                                                                                                                                 |  |  |  |

| 4             | TTINC    | W   | 0     | Setting this bit will increment the Time Tag Counter by "1" LSB when Time Tag Resolution bits 9-7 of Configuration Register #2 are set to "110".                                                                                                                                                                                                                  |  |  |  |

| 3             | TTRST    | W   | 0     | Setting TTRST to logic "1" will reset the Time Tag Counter.                                                                                                                                                                                                                                                                                                       |  |  |  |

| 2             | INTRST   | W   | 0     | Setting this bit will clear Interrupt Status Registers #1 and #2.                                                                                                                                                                                                                                                                                                 |  |  |  |

| 1             | BCMTSTRT | W   | 0     | In BC Mode, setting this bit will start the BC. In MT Mode, setting this bit will start the MT.                                                                                                                                                                                                                                                                   |  |  |  |

| 0 (LSB)       | SFTRESET | W   | 0     | Setting this bit will initiate a software reset.                                                                                                                                                                                                                                                                                                                  |  |  |  |

### 2.6. BC Control Word Register, Read/Write 0x0004

The BC Control Word is the first word in each Message Control / Status Block. The BC Control Word is not transmitted on the MIL-STD-1553 bus. This word is initialized and maintained by the host to specify message attributes such as bit masks for the received RT Status Word, which bus to use, enabling self test, BC message format, etc.

| Bit No.  | Mnemonic | R/W | Reset | Bit Description                                                                                                                                                               |

|----------|----------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |          |     |       | Transmit Time Tag for Synchronize (with data) Mode Code Command (MC17).                                                                                                       |

| 15 (MSB) | TXTTMC17 | R/W | 0     | If TXTTMC17 bit is logic "0" the BC transmits the value contained in the Message Data Block as the data word for a "synchronize" mode code command MC17.                      |

|          |          |     |       | If TXTTMC17 bit is logic "1", the "synchronize" mode data word value originates from the value of the Time Tag Register. Bit 5 of Configuration Register #2 must also be set. |

|          |          |     |       | Message Error Bit Mask.                                                                                                                                                       |

| 14       | MEMASK   | R/W | 0     | If MEMASK bit is logic "0" and the Message Error bit is logic 1 in the received RT Status Word, the BC will recognise the Message Error status.                               |

|          |          |     |       | If MEMASK bit is logic "1", the Message Error bit in the received RT Status Word is masked and is treated by the BC as "Don't Care".                                          |

|          | SRQMASK  | R/W | 0     | Service Request Bit Mask.                                                                                                                                                     |

| 13       |          |     |       | If SRQMASK bit is logic "0" and the Service Request bit is logic 1 in the received RT Status Word, the BC will recognise the Service Request status.                          |

|          |          |     |       | If SRQMASK bit is logic "1", the Service Request bit in the received RT Status Word is masked and is treated by the BC as "Don't Care".                                       |

|          |          |     |       | Busy Bit Mask.                                                                                                                                                                |

| 12       | BSYMASK  | R/W | 0     | If BSYMASK bit is logic "0" and the Busy bit is logic 1 in the received RT Status Word, the BC will recognise the Busy status.                                                |

|          |          |     |       | If BSYMASK bit is logic "1", the Busy bit in the received RT Status Word is masked and is treated by the BC as "Don't Care".                                                  |

|          |          |     |       | Subsystem Flag Bit Mask.                                                                                                                                                      |