# HI-6260

MIL-STD-1553 Simple System Remote Terminal (SSRT)

December 2019

#### 1. Overview

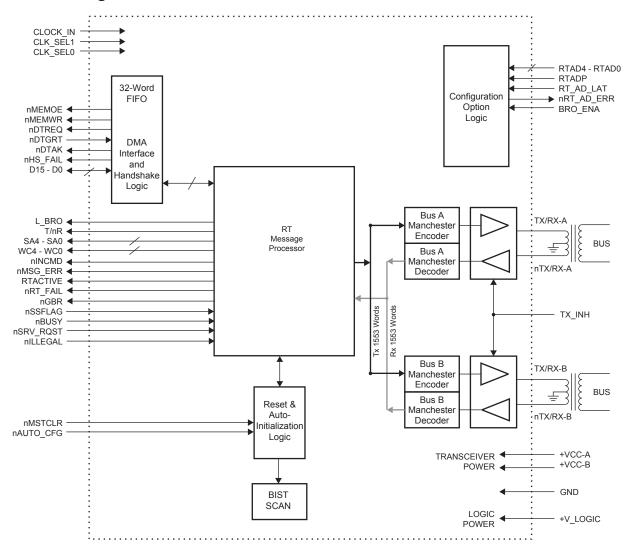

The HI-6260CQ family is a fully integrated and dual redundant MIL-STD-1553 Simple System Remote Terminal (SSRT) solution which includes 1553 protocol and dual transceivers in a single package. The device is a direct pin compatible drop-in replacement for the Data Device Corporation (DDC®) Mini-ACE® Mark3 SSRT family of MIL-STD-1553 Terminals.

### 1.1. Simple System Remote Terminal (SSRT)

The SSRT provides a MIL-STD-1553 Remote Terminal interface for a simple system that doesn't have or usually require a microprocessor. It therefore provides a lower cost alternative to a traditional RT-only device with a microprocessor host interface. Communication is achieved via a DMA interface with a handshake data transfer mechanism. The device includes a 32-word deep FIFO for received messages and supports all MIL-STD-1553 message types, including mode codes. Any subset of the possible 1553 commands may be optionally illegalized by utilizing an illegalization table in an external RAM, or on a command-by-command basis by asserting the ILLEGAL input signal.

The RT will ignore invalid commands and only valid words will be stored in the FIFO. In addition, the device has a number of output signals which provide real-time status monitoring for events such as message errors, handshake failure, loopback test failure or transmitter timeout.

The RT address and parity are programmed directly via six input pins. An additional input signal is available to internally latch the RT address and an output signal is provided to indicate a parity error.

The SSRT provides an autonomous built-in self-test capability, which is automatically initiated following power turn-on or after the terminal has received an "Initiate Self-Test" mode command. The built-in self-test may be disabled via the auto-configuration feature, which also allows various other features to be enabled or disabled at start-up.

Note: DDC<sup>®</sup>, Mini-ACE®, Enhanced Mini-ACE®, Micro-ACE®, Mini-ACE® Mark3 and Total-ACE® are registered trademarks of Data Device Corporation, Bohemia, NY, USA. There is no affiliation between Data Device Corporation and Holt Integrated Circuits Inc.

#### **Overview**

#### 1.2. Features

- Fully Integrated Remote Terminal including dual 3.3V or 5V transceivers

- MIL-STD-1553A/B/1760 Compliant

- · 32-Word Internal FIFO with burst mode capability

- 16-Bit DMA Interface

- External RT Address Inputs

- Built-in Self-Test

- Auto-Configuration Capability

- -40°C to +85°C or -55°C to +125°C

- 80-Pin Hermetic Gull Wing Package

- o 22.4mm x 22.4mm x 3.6mm

## 1.3. Application Benefits

- Simplified Board Design and Layout

- Third Party RT Validated

- Single Die for Improved Reliability

- Cost Effective Direct Drop-in Replacement for DDC® Mini-ACE® Mark3 SSRT Family

#### 1.4. Cross Reference Guide

| Holt P/N    | DDC® P/N       |

|-------------|----------------|

| HI-62605CQx | BU-64703G3-xxx |

| HI-62603CQx | BU-64703GC-xxx |

## 1.5. Block Diagram

## 1.6. Loopback Test

The SSRT automatically performs a digital loopback self-test following every non-broadcast message and checks the message for validity. The internal receiver for the same bus is independent from the encoder logic used for bus transmission and the receiver detects and decodes the received replica of the transceiver's own transmission. The digital signal paths used for encoding and transmission (as well as reception and decoding) are fully tested without involving the external MIL-STD-1553 bus. If the loopback test fails, the Terminal Flag bit will be set in the SSRT status word for the next non-broadcast message.

#### 1.7. Protocol Self-Test

The SSRT has the ability to perform a self-test of its internal protocol logic, including all registers and the internal FIFO. The test duration is about 32,000 clock cycles. During self-test, the SSRT will not respond to any messages received from the 1553 bus.

The protocol self-test may be run at power-up by asserting both the RSTBITEN input signal and Auto Configuration Parameter bit 5 to logic "1". The self-test will also be run if the device receives an Initiate Self-Test mode command from the 1553 bus.

If the protocol self-test fails, the Terminal Flag bit will be set in the SSRT status word. The BISTF, bit 8 in the BIST Word will also be set and the SSRT's RTFAIL output signal will be asserted to logic "0".

## 1.8. Built-In Self-Test (BIST) Word

The SSRT automatically populates a Built-In Self-Test Word, whose bits will read logic "1" to reflect errors flagged by the device. This word will be transmitted to the BC following a "Transmit BIT Word" mode command. The BIST word bit descriptions are provided below in Table 1.

Table 1. Internal Built-in Self Test (BIST) Word Definition

| Bit No.  | Mnemonic   | R/W  | Reset | Bit Description                                                                                                                                     |

|----------|------------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 (MSB) | ТХТО       | R    | 0     | Transmitter Timed Out.                                                                                                                              |

| 10 (WOB) | 17(10      | _ `` |       | The transmitter timeout of 660.5µs was exceeded.                                                                                                    |

| 14       | LBFB       | R    | 0     | Loopback Test Failure B.                                                                                                                            |

| 14       | LDI D      | _ `` |       | A loopback failure occurred on Bus B.                                                                                                               |

| 13       | LBFA       | R    | 0     | Loopback Test Failure A.                                                                                                                            |

| 13       | LDIA       | '`   | 0     | A loopback failure occurred on Bus A.                                                                                                               |

| 12       | HSF        | R    | 0     | This bit will be set if the system fails to assert a Data Transfer Grant DTGRT within 10µs of the SSRT requesting a data transfer (DTREQ asserted). |

|          |            |      |       | Transmitter Shutdown B.                                                                                                                             |

| 11       | 11 TXSDB R |      | 0     | A Transmitter Shutdown mode command was received on Bus A. This mode command shuts down the transmitter of the inactive bus.                        |

|          |            |      |       | Transmitter Shutdown A.                                                                                                                             |

| 10       | TXSDA      | R    | ₹ 0   | A Transmitter Shutdown mode command was received on Bus B. This mode command shuts down the transmitter of the inactive bus.                        |

| 9        | TFINH      | R    | 0     | Terminal Flag Inhibited.                                                                                                                            |

| 9        | TEINIT     |      | U     | An Inhibit Terminal Flag mode command was received.                                                                                                 |

| 8        | BISTF      | R    | 0     | BIST Test Fail.                                                                                                                                     |

| 0        | ыотг       |      | U     | The device failed its internal Built-In Self-Test routine.                                                                                          |

|          |            |      |       | Data Word Count High.                                                                                                                               |

| 7        | DWCH       | R    | 0     | The number of data words received in the last message was higher than expected.                                                                     |

|          |            |      |       | Data Word Count Low.                                                                                                                                |

| 6        | DWCL       | R    | 0     | The number of data words received in the last message was lower than expected.                                                                      |

| 5        | SNYCF      | R    | 0     | Incorrect Sync Received.                                                                                                                            |

|          | SINTOF     | '`   | U     | A command sync bit was detected in a data word.                                                                                                     |

| 4        | INVW       | R    | 0     | Invalid Word Received                                                                                                                               |

| Bit No. | Mnemonic | R/W | Reset | Bit Description                                                                                                                                                                            |

|---------|----------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |          |     |       | RT-to-RT Gap / Sync / Address Error.                                                                                                                                                       |

| 3       | RTRTE    | R   | 0     | If the device is the receiving RT in an RT-to-RT transfer, this bit will be set if there is a gap time error (gap less than 2µs), incorrect sync or format error, or incorrect RT address. |

|         |          |     |       | RT-to-RT Timeout Error.                                                                                                                                                                    |

| 2       | RTRTTO   | R   | 0     | This bit will be set if the allowed RT-to-RT response time of about 17µs is exceeded.                                                                                                      |

|         |          |     |       | RT-to-RT Command Word Error .                                                                                                                                                              |

| 1       | RTRTCWE  | R   | 0     | If the device is the receiving RT in an RT-to-RT transfer, this bit will be set if there is an error in the Transmit Command Word, e.g. $T/\overline{R}$ bit is not logic "1".             |

| 0 (LSB) | RXCWE    | R   | 0     | Received Command Word Error.                                                                                                                                                               |

| U (LOD) | INCOVE   |     | U     | This bit will be set if there is an error in a received Command Word.                                                                                                                      |

## 1.9. Auto-Configuration

Auto-Configuration is controlled using the AUTO\_CFG input signal and allows six optional features to be enabled or disabled. Enabling or disabling each feature is controlled by the Auto-Configuration Parameters described below in Table 2.

If AUTO\_CFG is connected to logic "1", then the auto-configuration is disabled and the six configuration parameters will be their default values of logic "1".

If  $\overline{AUTO\_CFG}$  is connected to logic "0", then the configuration parameters are transferred over the data lines D5-D0 using a DMA data transfer.

Table 2. Auto-Configuration Parameters

| Bit No. | Mnemonic    | R/W    | Default | Bit Description                                                                                                                                                                                                                                                                                                                     |

|---------|-------------|--------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5       | RTSTF       | R/W    | 1       | If RTSTF is logic "1" (default) then the RT will go online if the Built-<br>In Self-Test fails.                                                                                                                                                                                                                                     |

| 5       | KISIF       | FK/VV  | ı       | If RTSTF is logic "0", then the RT will go online only if the Built-In Self-Test passes.                                                                                                                                                                                                                                            |

| 4       | TFLBKF      | R/W    | 1       | If TFLBKF is logic "1" (default), then the Terminal Flag bit will be set in the SSRT status word for the next non-broadcast message.                                                                                                                                                                                                |

| 4       | IFLDKF      | FC/ VV | ı       | If TFLBKF is logic "0", then the Terminal Flag bit will not be set in the SSRT status word.                                                                                                                                                                                                                                         |

| 3       | 1552D       | R/W    | 4       | If 1553B is logic "1" (default), then the SSRT operates in MIL-STD-1553B mode.                                                                                                                                                                                                                                                      |

| 3       | 1553B       | FK/VV  | 1       | If 1553B is logic "0", then the SSRT operates in MIL-STD-1553A mode.                                                                                                                                                                                                                                                                |

| 2       | SUB30 R/W 1 |        | 1       | If SUB30 is logic "1" (default), then all data words for a receive command to subaddress 30 will be stored in the internal FIFO and not transferred to the external system. When a transmit command is subsequently received for subaddress 30, the data words will be read directly from the FIFO, instead of the external system. |

|         |             |        |         | If SUB30 is logic "0", then all data words for a receive command to subaddress 30 will be transferred to the external system.                                                                                                                                                                                                       |

| 1       | BURST       | R/W    | 1       | If BURST is logic "1" (default), then Burst Mode is enabled. In Burst Mode, for a receive message, all received data words will be first stored in the internal FIFO and sent to the external system contiguously following reception of the last data word.                                                                        |

|         |             |        |         | If BURST is logic "0", Burst Mode is disabled. Each received data word is transferred to the external system as it is received, requiring a DMA handshake for each data word.                                                                                                                                                       |

| 0 (LSB) | BIST        | R/W    | 1       | If both the RSTBITEN input signal and the BIST parameter are logic "1" (default), then the SSRT will run the Built-In Self-Test on power-up following the rising edge of MSTCLR.                                                                                                                                                    |

|         |             |        |         | If etiher RSTBITEN or BIST are logic "0", then Built-In Self-Test is disabled.                                                                                                                                                                                                                                                      |

# 1.10. Clock Input

The supported clock frequencies are selected by the input signals CLK\_SEL\_1 and CLK\_SEL\_0, as shown in Table 3.

Table 3. Clock Frequency Selection

| CLK_SEL_1 | CLK_SEL_0 | Clock Frequency |

|-----------|-----------|-----------------|

| 0         | 0         | 10 MHz          |

| 0         | 1         | 20 MHz          |

| 1         | 0         | 12 MHz          |

| 1         | 1         | 16 MHz          |

# 2. Timing Diagrams

**NOTE:** \* L\_BRO and  $T/\overline{R}$  show the same waveform.

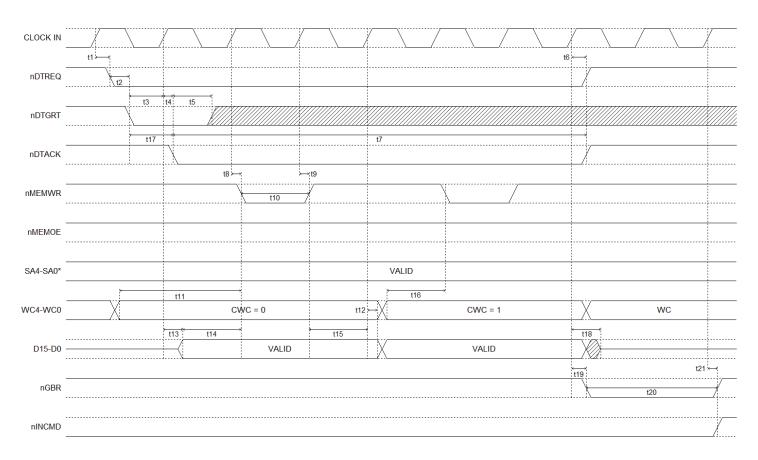

Figure 1. DMA Write Transfer (Burst Mode) Timing for Two Data Words

Table 4. DMA Write (Burst Mode) Timing for two data words

|      | Description                                         | Clock     | Response @ 5V |      |      | Resp | Unite |      |       |

|------|-----------------------------------------------------|-----------|---------------|------|------|------|-------|------|-------|

| Time | Description                                         | Frequency | Min.          | Тур. | Max. | Min. | Тур.  | Max. | Units |

| t1   | CLOCK IN rising edge to DTREQ falling edge          | All       |               |      | 40   |      |       | 40   | ns    |

| t2   | DTREQ falling edge to DTGRT falling edge            | All       |               |      | 10   |      |       | 10   | μs    |

| t3   | DTGRT low setup time to CLOCK IN rising edge        | All       | 10            |      |      | 15   |       |      | ns    |

| t4   | CLOCK IN rising edge to DTACK falling edge          | All       |               |      | 40   |      |       | 40   | ns    |

| t5   | DTGRT hold time from DTACK falling edge             | All       |               |      | 30   |      |       | 30   | ns    |

| t6   | CLOCK IN rising edge to DTREQ and DTACK rising edge | All       |               |      | 30   |      |       | 40   | ns    |

|      |                                                     | 20 MHz    | 290           | 300  |      | 290  | 300   |      | ns    |

| t7   | DTACK low pulse width                               | 16 MHz    | 365           | 375  |      | 365  | 375   |      | ns    |

| 17   | DTACK low pulse width                               | 12 MHz    | 490           | 500  |      | 490  | 500   |      | ns    |

|      |                                                     | 10 MHz    | 590           | 600  |      | 590  | 600   |      | ns    |

| t8   | CLOCK IN rising edge to MEMWR falling edge          | All       |               |      | 40   |      |       | 40   | ns    |

| t9   | CLOCK IN rising edge to MEMWR rising edge           | All       |               |      | 30   |      |       | 40   | ns    |

|      |                                                     | 20 MHz    | 40            | 50   |      | 40   | 50    |      | ns    |

| t10  | MEMWR low pulse width                               | 16 MHz    | 52.5          | 62.5 |      | 52.5 | 62.5  |      | ns    |

| 110  |                                                     | 12 MHz    | 73.3          | 83.3 |      | 73.3 | 83.3  |      | ns    |

|      |                                                     | 10 MHz    | 90            | 100  |      | 90   | 100   |      | ns    |

|      |                                                     | 20 MHz    | 60            |      |      | 60   |       |      | ns    |

| t11  | CWC setup time to MEMWR falling edge (first         | 16 MHz    | 85            |      |      | 85   |       |      | ns    |

| '''  | word only)                                          | 12 MHz    | 127           |      |      | 127  |       |      | ns    |

|      |                                                     | 10 MHz    | 160           |      |      | 160  |       |      | ns    |

| t12  | Data output hold time from CLOCK IN rising edge     | All       | 10            |      |      | 15   |       |      | ns    |

| t13  | CLOCK IN rising edge delay to output data valid     | All       |               |      | 40   |      |       | 40   | ns    |

|      |                                                     | 20 MHz    | 10            |      |      | 10   |       |      | ns    |

| 44.4 | Data output setup time to MEMWR falling             | 16 MHz    | 22            |      |      | 22   |       |      | ns    |

| t14  | edge                                                | 12 MHz    | 43            |      |      | 43   |       |      | ns    |

|      |                                                     | 10 MHz    | 60            |      |      | 60   |       |      | ns    |

|      |                                                     | Clock     | Resp | Response @ 5V |      |      | Response @ 3.3V |      |       |

|------|-----------------------------------------------------|-----------|------|---------------|------|------|-----------------|------|-------|

| Time | Description                                         | Frequency | Min. | Тур.          | Max. | Min. | Тур.            | Max. | Units |

|      |                                                     | 20 MHz    | 20   |               |      | 10   |                 |      | ns    |

| t15  | Data output and CWC hold time from MEMWR            | 16 MHz    | 33   |               |      | 23   |                 |      | ns    |

| 115  | rising edge                                         | 12 MHz    | 53   |               |      | 43   |                 |      | ns    |

|      |                                                     | 10 MHz    | 70   |               |      | 60   |                 |      | ns    |

|      |                                                     | 20 MHz    | 10   |               |      | 10   |                 |      | ns    |

| t16  | CWC setup time to MEMWR falling edge                | 16 MHz    | 23   |               |      | 23   |                 |      | ns    |

| 116  | (except first word)                                 | 12 MHz    | 43   |               |      | 43   |                 |      | ns    |

|      |                                                     | 10 MHz    | 60   |               |      | 60   |                 |      | ns    |

|      | DTGRT falling edge to DTACK falling edge            | 20 MHz    |      |               | 100  |      |                 | 105  | ns    |

| t17  |                                                     | 16 MHz    |      |               | 113  |      |                 | 118  | ns    |

| 117  |                                                     | 12 MHz    |      |               | 133  |      |                 | 138  | ns    |

|      |                                                     | 10 MHz    |      |               | 150  |      |                 | 155  | ns    |

| t18  | CLOCK IN rising edge delay to output data tri-state | All       |      |               | 40   |      |                 | 40   | ns    |

| t19  | CLOCK IN rising edge to GBR falling edge            | All       |      |               | 40   |      |                 | 40   | ns    |

|      |                                                     | 20 MHz    | 90   | 100           |      | 90   | 100             |      | ns    |

| t20  | GBR low pulse width                                 | 16 MHz    | 115  | 125           |      | 115  | 125             |      | ns    |

| 120  | GBK low pulse width                                 | 12 MHz    | 157  | 167           |      | 157  | 167             |      | ns    |

|      |                                                     | 10 MHz    | 190  | 200           |      | 190  | 200             |      | ns    |

| t21  | INCMD rising edge from CLOCK IN rising edge         | All       |      |               | 30   |      |                 | 40   | ns    |

**NOTE:** \* L\_BRO and  $T/\overline{R}$  show the same waveform.

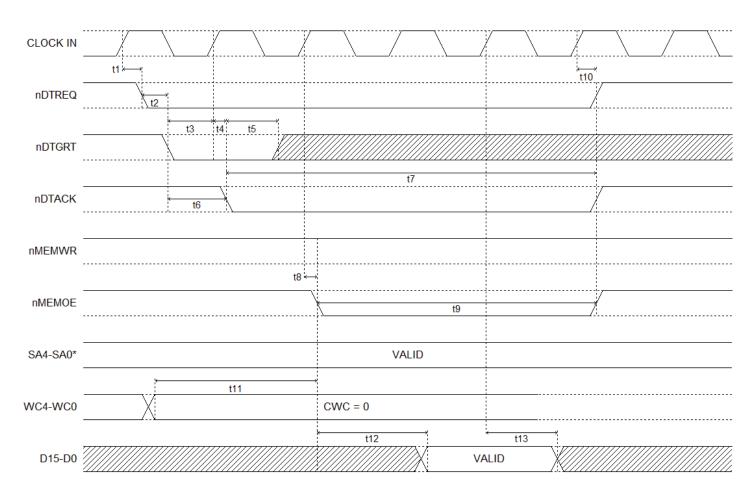

Figure 2. DMA Read Transfer Timing (Single Word)

Table 5. DMA Read Transfer Timing

| T'   | Description                                                | Clock     | Resp | oonse | @ 5V | Response @ 3.3V |      |      | 11    |

|------|------------------------------------------------------------|-----------|------|-------|------|-----------------|------|------|-------|

| Time | Description                                                | Frequency | Min. | Тур.  | Max. | Min.            | Тур. | Max. | Units |

| t1   | CLOCK IN rising edge to DTREQ falling edge                 | All       |      |       | 40   |                 |      | 40   | ns    |

| t2   | DTREQ falling edge to DTGRT falling edge                   | All       |      |       | 10   |                 |      | 10   | μs    |

| t3   | DTGRT low setup time to CLOCK IN rising edge               | All       |      |       | 10   |                 |      | 10   | ns    |

| t4   | CLOCK IN rising edge to DTACK falling edge                 | All       |      |       | 40   |                 |      | 40   | ns    |

| t5   | DTGRT hold time from DTACK falling edge                    | All       |      |       | 30   |                 |      | 30   | ns    |

|      | DISKT Hold time from DTACK falling edge                    |           |      |       | 100  |                 |      | 105  | ns    |

| 40   | DTODT fallings advanta DTACK fallings advan                | 16 MHz    |      |       | 113  |                 |      | 118  | ns    |

| t6   | DTGRT falling edge to DTACK falling edge                   | 12 MHz    |      |       | 133  |                 |      | 138  | ns    |

|      |                                                            | 10 MHz    |      |       | 150  |                 |      | 155  | ns    |

|      |                                                            | 20 MHz    |      | 200   |      |                 | 200  |      | ns    |

| 47   | DTACK low pulse width                                      | 16 MHz    |      | 250   |      |                 | 250  |      | ns    |

| t7   |                                                            | 12 MHz    |      | 333   |      |                 | 333  |      | ns    |

|      |                                                            | 10 MHz    |      | 400   |      |                 | 400  |      | ns    |

| t8   | CLOCK IN rising edge to MEMOE falling edge                 | All       |      |       | 40   |                 |      | 40   | ns    |

|      |                                                            | 20 MHz    |      | 150   |      |                 | 150  |      | ns    |

| 40   | MEMOE law and a midth                                      | 16 MHz    |      | 188   |      |                 | 188  |      | ns    |

| t9   | MEMOE low pulse width                                      | 12 MHz    |      | 250   |      |                 | 250  |      | ns    |

|      |                                                            | 10 MHz    |      | 300   |      |                 | 300  |      | ns    |

| t10  | CLOCK IN rising edge to DTREQ, DTACK and MEMOE rising edge | All       |      |       | 30   |                 |      | 40   | ns    |

|      |                                                            | 20 MHz    | 60   |       |      | 60              |      |      | ns    |

| 144  | CWC setup time to MEMOE falling edge                       | 16 MHz    | 85   |       |      | 85              |      |      | ns    |

| t11  | CWC setup time to MEMOE failing edge                       | 12 MHz    | 127  |       |      | 127             |      |      | ns    |

|      |                                                            | 10 MHz    | 160  |       |      | 160             |      |      | ns    |

|      |                                                            | 20 MHz    |      |       | 80   |                 |      | 70   | ns    |

| 140  | Input data valid delay from falling edge of                | 16 MHz    |      |       | 105  |                 |      | 95   | ns    |

| t12  | MEMOE                                                      | 12 MHz    |      |       | 146  |                 |      | 136  | ns    |

|      |                                                            | 10 MHz    |      |       | 180  |                 |      | 170  | ns    |

# **Timing Diagrams**

| Time |             | Description                                    | Clock | Resp | onse | @ 5V | Resp | Unito |       |    |

|------|-------------|------------------------------------------------|-------|------|------|------|------|-------|-------|----|

| Time | Description | Frequency                                      | Min.  | Тур. | Max. | Min. | Тур. | Max.  | Units |    |

| t    | 13          | Data input hold time from CLOCK IN rising edge | All   | 30   |      |      | 30   |       |       | ns |

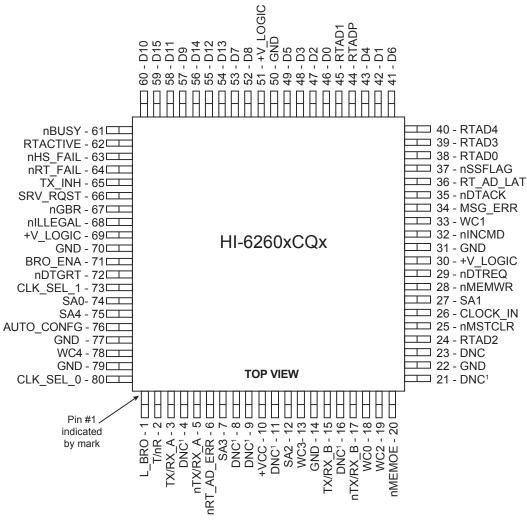

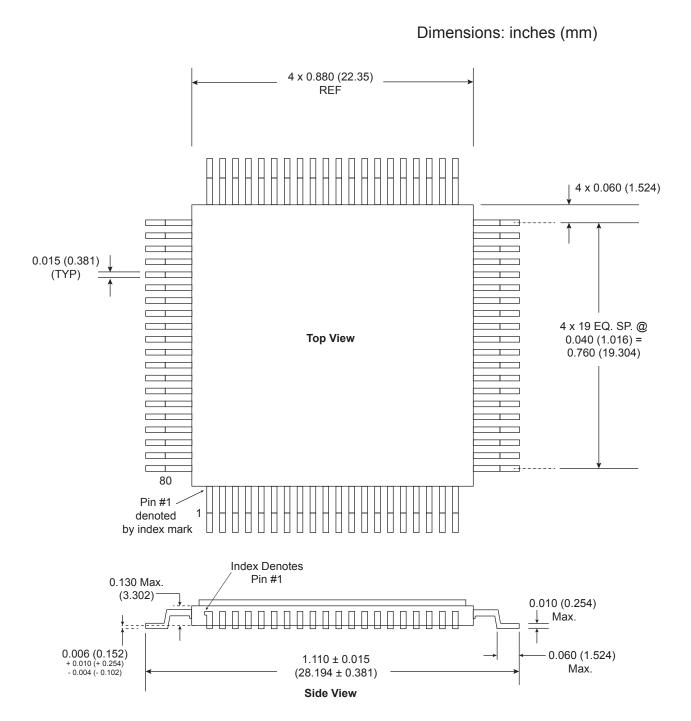

## 3. Pin Diagrams

#### Notes:

- 1. Do Not Connect (Factory test pin).

- 2. Prefix "n" denotes an inverted or negative signal, e.g. nMSTCLR =  $\overline{\text{MSTCLR}}$ , etc.

Figure 3. HI-6260xCQx Gull Wing Package Pinouts

# 4. Pin Descriptions

Table 6. Power and Ground

| Signal Name | Function     | Description                                                                                 |

|-------------|--------------|---------------------------------------------------------------------------------------------|

| +VCC        | Power Supply | 3.3V or 5.0V DC power supply for transceiver. 3.3V for HI-62603CQxx. 5.0V for HI-62605CQxx. |

| +V_LOGIC    | Power Supply | DC power supply for digital logic. This pin supports both 3.3V or 5V logic supplies.        |

| GND         | Power Supply | Power supply ground.                                                                        |

Table 7. MIL-STD-1553 Isolation Transformer Connections

| Signal Name | Function   | Description                                                  |

|-------------|------------|--------------------------------------------------------------|

| TX/RX-A     | Analog I/O | Bi-directional Bus A interface to external MIL-STD-1553      |

| TX/RX-A     | Analog I/O | isolation transformer. Observe positive / negative polarity. |

| TX/RX-B     | Analog I/O | Bi-directional Bus B interface to external MIL-STD-1553      |

| TX/RX-B     | Analog I/O | isolation transformer. Observe positive / negative polarity. |

Table 8. Data and Command/Address Busses

| Signal Name             | Function                       | Description                                                                                                                                                                                                                                       |

|-------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D15 (MSB) - D0<br>(LSB) | Data inputs or<br>Data outputs | Bi-directional data bus for host read/write operations on registers and RAM.                                                                                                                                                                      |

| L_BRO                   | Digital Output                 | This output signal indicates receipt of a broadcast command (logic "1").  If a non-broadcast command is received, this signal will logic "0".                                                                                                     |

| T/R                     | Digital Output                 | This output signal indicates if a received command is a transmit command (logic "1") or a receive command (logic "0").                                                                                                                            |

| SA4 - SA0               | Digital Outputs                | These 5 output signals indicate the value of the subaddress in the received command word                                                                                                                                                          |

|                         | · WC0 Digital Outputs          | Initially, when a new command word is received, output signals WC[4:0] will indicate the value of the Word Count or Mode Code field of the received command word.                                                                                 |

| WC4 - WC0               |                                | For Mode Code commands, the value of the mode code field will be latched until the next command word is received.                                                                                                                                 |

| VVC4 - VVCU             |                                | For non-Mode Code commands, the WC[4:0] signals will be updated to reflect the current data word count as each data word is transferred to the system (receive command) or read from the system and transferred to the device (transmit command). |

Table 9. DMA Interface Signals

| Signal Name | Function       | Description                                                                                                                                                                                |

|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DTREQ       | Digital Output | This active low output is a handshake signal used by the device to request access to the external data bus. The handshake is complete when the DTGRT input signal is asserted in response. |

| DTGRT       | Digital Input  | This input signal completes the handshake following a DTREQ request and is asserted to indicate that control of the data bus has been released to the device.                              |

| DTACK       | Digital Output | This active low output is asserted to acknowledge a data transfer grant (DTGRT) and indicates that the device has accepted control of the external data bus D[15:0].                       |

| HS_FAIL     | Digital Output | Handshake Fail.  This output signal will be asserted low when a DTGRT (Data Transfer Grant) signal is not received in time following a DTREQ (Data Transfer Request).                      |

| MEMOE       | Digital Output | This signal will be asserted low for three clock cycles as each data word is read from the external system.                                                                                |

| MEMWR       | Digital Output | This signal will be asserted low during write cycles to the external system.                                                                                                               |

Table 10. RT Address

| Signal Name              | Function      | Description                                                                                                                                                                                                                                                                                                                                     |

|--------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTAD4 (MSB)              | Digital Input |                                                                                                                                                                                                                                                                                                                                                 |

| RTAD3                    | Digital Input |                                                                                                                                                                                                                                                                                                                                                 |

| RTAD2                    | Digital Input | RT Address Input signals.                                                                                                                                                                                                                                                                                                                       |

| RTAD1                    | Digital Input |                                                                                                                                                                                                                                                                                                                                                 |

| RTAD0 (LSB)              | Digital Input |                                                                                                                                                                                                                                                                                                                                                 |

| RTADP                    | Digital Input | Remote Terminal Address Parity.  Used to provide odd parity for the RT address on RTAD[4:0].                                                                                                                                                                                                                                                    |

| RT_AD_LAT                | Digital Input | RT Address Latch.  This input signal is used to control how the RT address is latched internally. If RT_AD_LAT is logic "0", then the RT address and parity will simply track RTAD4:0 and RTADP inputs.  If RT_AD_LAT transitions from logic "0" to logic "1", the values on RTAD4:0 and RTADP will be latched on the rising edge of RT_AD_LAT. |

| RT_AD_ERR Digital Output |               | If this output is logic "0", it indicates the correct parity was not provided between RTAD[4:0] and RTADP inputs.  If this output is logic "1", correct (odd) parity was provided between RTAD[4:0] and RTADP inputs.                                                                                                                           |

Table 11. RT Status Word Inputs

| Signal Name | Function      | Description                                                                                                                                                                                                                                                                                   |

|-------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ILLEGAL     | Digital Input | Commands may be illegalized on an individual basis by asserting this input (logic "0").  In this case, the Message Error bit in the transmitted RT Status Word will be logic "1".  If this input is logic "1", the Message Error bit in the transmitted RT Status Word will remain logic "0". |

| SRV_RQST    | Digital Input | If this input is logic "0", the Service request bit in the transmitted RT Status Word will be logic "1".  If this input is logic "1", the Service request bit in the transmitted RT Status Word will be logic "0".                                                                            |

| SSFLAG      | Digital Input | If asserted (logic "0"), the Subsystem Flag bit will be set in the transmitted RT Status Word.                                                                                                                                                                                                |

| BUSY        | Digital Input | If asserted (logic "0"), the Busy bit will be set to logic "1" in the transmitted RT Status Word.                                                                                                                                                                                             |

Table 12. RT Status Signals

| Signal Name | Function            | Description                                                                                                                               |

|-------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| RTACTIVE    | ΓΙVE Digital Output | This output signal will be logic "1" when the RT is active and communicating with the MIL-STD-1553 bus.                                   |

| RIACTIVE    |                     | This signal will remain logic "0" while the RT is executing a built-in self test or during auto configuration.                            |

| INCMD       | Digital Output      | INCMD is asserted low whenever a message is in progress.                                                                                  |

| GBR         | Digital Output      | This output signal will be asserted low for two clock cycles whenever a valid command is received and transferred to the external system. |

| MSG ERR     | Digital Output      | This output signal will be asserted low to indicate the RT detected a message error on the 1553 bus.                                      |

| MSG_ERR     | Digital Output      | MSG_ERR will be cleared (logic "1") when the next valid command is received or upon assertion of MSTCLR.                                  |

| RT_FAIL     | Digital Output      | This output signal will be asserted low when the RT failed its built-in self-test.                                                        |

Table 13. Reset and Control Inputs

| Signal Name | Function               |                                                                                                                                                                                                                                                      | Description     |           |  |  |

|-------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------|--|--|

| MSTCLR      | Digital Input          | Active low Reset input.                                                                                                                                                                                                                              |                 |           |  |  |

| AUTO_CFG    | Digital Input          | If this input is logic "0", then auto configuration is enabled.  Auto configuration is performed following assertion of MSTCLR by a DMA read transfer over data bus inputs D[5:0].  If this input is logic "0", then auto configuration is disabled. |                 |           |  |  |

| BRO_ENA     | Digital Input          | Broadcast Enable.  Setting this bit to logic "1" will enable broadcast commands, i.e. RT address 31 wi recognized as the broadcast subaddress.                                                                                                       |                 |           |  |  |

| TX_INH      | Digital Input          | Setting this input to logic "1" will force both BUS A and BUS B transmitters to shutdown.                                                                                                                                                            |                 |           |  |  |

|             | CLOCK_IN Digital Input | 20 MHz, 16 MHz, 12 MHz, or 10 MHz clock input signal.  The frequency must be specified by the CLK_SEL_1 and CLK_SEL_0 inputs as follows:                                                                                                             |                 |           |  |  |

|             |                        | CLK_SEL_1 Input                                                                                                                                                                                                                                      | CLK_SEL_0 Input | Frequency |  |  |

| CLOCK_IN    |                        | 0                                                                                                                                                                                                                                                    | 0               | 10 MHz    |  |  |

|             |                        | 0                                                                                                                                                                                                                                                    | 1               | 20 MHz    |  |  |

|             |                        | 1                                                                                                                                                                                                                                                    | 0               | 12 MHz    |  |  |

|             |                        | 1                                                                                                                                                                                                                                                    | 1               | 16 MHz    |  |  |

## 5. Electrical Characteristics

## 5.1. Absolute Maximum Ratings

|                               | Logic +3.3V                           | -0.3 V to +6.0 V |  |

|-------------------------------|---------------------------------------|------------------|--|

| Cupply voltages               | Transceivers +3.3V (not transmitting) | -0.3 V to +6.0 V |  |

| Supply voltages               | Transceivers +3.3V (transmitting)     | -0.3 V to +4.5 V |  |

|                               | Transceivers +5V                      | -0.3 V to +7.0 V |  |

| Logic input voltage range     | -0.3 V to +6.0 V                      |                  |  |

| Receiver differential voltage |                                       | 10 Vp-p          |  |

| Solder Temperature (reflow)   |                                       | 260°C            |  |

| Junction Temperature          | 175°C                                 |                  |  |

| Storage Temperature           | -65°C to +150°C                       |                  |  |

# 5.2. Recommended Operating Conditions

| Parameters        |                   |      | Limits |      |    |  |

|-------------------|-------------------|------|--------|------|----|--|

| Paran             | Min               | Тур  | Max    | Unit |    |  |

|                   | Logic             | 3.0  | 3.3    | 3.6  | V  |  |

| Supply Voltages   | 3.3V Transceivers | 3.14 | 3.3    | 3.46 | V  |  |

|                   | 5.0V Transceivers | 4.75 | 5.0    | 5.25 | V  |  |

| Tomporatura Danga | Industrial        | -40  |        | 85   | °C |  |

| Temperature Range | Extended          | -55  |        | 125  | °C |  |

## 5.3. DC Electrical Characteristics

$T_{A}$  = Operating Temperature Range

|                                 |                                    |                    | Symbol Conditions                                                                       |      | Limits |      |                 |

|---------------------------------|------------------------------------|--------------------|-----------------------------------------------------------------------------------------|------|--------|------|-----------------|

| Paramete                        | ers                                | Symbol             | Conditions                                                                              | Min  | Тур    | Max  | Unit            |

| Power Supply                    |                                    |                    |                                                                                         |      |        |      |                 |

|                                 | 3.3V Logic                         | V <sub>Logic</sub> |                                                                                         | 3.0  | 3.3    | 3.6  | V               |

| Operating Supply Voltages       | 3.3V Transceivers                  | V <sub>DD</sub>    |                                                                                         | 3.14 | 3.3    | 3.46 | V               |

|                                 | 5.0V Transceivers                  | V <sub>DD</sub>    |                                                                                         | 4.75 | 5.0    | 5.25 | V               |

|                                 |                                    | I <sub>CC1</sub>   | Not Transmitting                                                                        | -    | -      | 15   | mA              |

| Power Supply Current See Note 1 | $V_{LOGIC} = 3.3V$ $V_{DD} = 5.0V$ | I <sub>CC2</sub>   | Continuous supply current while one bus transmits @ 50% duty cycle, 70Ω resistive load  | ı    | -      | 330  | mA              |

|                                 | DD DD                              | I <sub>CC23</sub>  | Continuous supply current while one bus transmits @ 100% duty cycle, 70Ω resistive load | -    | -      | 565  | mA              |

|                                 |                                    | PD <sub>1</sub>    | Not Transmitting                                                                        | -    | -      | 60   | mW              |

| Power Dissipation See Note 2    | $V_{LOGIC} = 3.3V$ $V_{DD} = 5.0V$ | PD <sub>2</sub>    | Transmit one bus @ 50% duty cycle, 70Ω resistive load                                   | -    | -      | 1.05 | W               |

|                                 | DD OIG                             | PD <sub>3</sub>    | Transmit one bus @ 100% duty cycle, 70Ω resistive load                                  | -    | -      | 1.55 | W               |

| Logic                           | -                                  | •                  | •                                                                                       |      |        |      |                 |

| Innut Valtage (High)            |                                    |                    | All digital inputs, except CLK <sub>IN</sub>                                            | 2.1  | -      | -    | V               |

| Input Voltage (High)            |                                    | V <sub>IH</sub>    | CLK <sub>IN</sub>                                                                       | 0.8  |        |      | V <sub>DD</sub> |

| Input Voltage (Low)             |                                    | V <sub>IL</sub>    | All digital inputs, except CLK <sub>IN</sub>                                            | -    | -      | 0.7  | V               |

| mpat voltage (20w)              |                                    | ▼ IL               | CLK <sub>IN</sub>                                                                       |      |        | 0.2  | V <sub>DD</sub> |

|                                 |                                    |                    | All digital inputs, except CLK <sub>IN</sub> ,                                          |      |        |      |                 |

| Input Current (High)            |                                    | I <sub>IH</sub>    | $V_{LOGIC} = 3.6V = V_{IH}$                                                             | -10  | -      | -10  | μA              |

|                                 |                                    | ,iH                | $V_{LOGIC} = 3.6V, V_{IH} = 2.7V$                                                       | -350 | -      | -33  | μA              |

|                                 |                                    |                    | CLK <sub>IN</sub>                                                                       | -10  | -      | 10   | μA              |

|                                 |                                    |                    | All digital inputs, except CLK <sub>IN</sub> ,                                          |      |        |      |                 |

| Input Current (Low)             |                                    | I <sub>IL</sub>    | $V_{LOGIC} = 3.6V, V_{IL} = 0.4V$                                                       | -350 | -      | -33  | μΑ              |

|                                 |                                    |                    | CLK <sub>IN</sub>                                                                       | -10  | -      | 10   | μA              |

| Output Voltage (High)           |                                    | V <sub>OH</sub>    | $V_{LOGIC} = 3.0V, V_{IH} = 2.7V,$<br>$V_{IL} = 0.2V, I_{OH} = max$                     | 2.4  | -      | -    | V               |

| Output Voltage (Low)            |                                    | V <sub>OL</sub>    | $V_{LOGIC} = 3.0V, V_{IH} = 2.7V,$<br>$V_{IL} = 0.2V, I_{OL} = max$                     | -    | -      | 0.4  | V               |

| Output Current (High)           |                                    | I <sub>oh</sub>    | V <sub>LOGIC</sub> = 3.0V                                                               | -    | -      | -2.2 | mA              |

| Output Current (Low)            |                                    | I <sub>OL</sub>    | V <sub>LOGIC</sub> = 3.0V                                                               | 2.2  | -      | -    | mA              |

| Para d                                             |                                     | Ormshall Canaditions |                                                  | Limits |       |      |       |

|----------------------------------------------------|-------------------------------------|----------------------|--------------------------------------------------|--------|-------|------|-------|

| Paramete                                           | ers                                 | Symbol               | Conditions                                       | Min    | Тур   | Max  | Unit  |

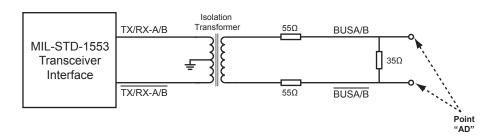

| RECEIVER (Measured at Point "                      | AD" in Figure 6 unless              | otherwise sp         | pecified)                                        |        |       |      |       |

| Input Resistance                                   |                                     | R <sub>IN</sub>      | Differential                                     | 20     | -     | -    | kΩ    |

| Input Capacitance                                  |                                     | C <sub>IN</sub>      | Differential                                     | -      | -     | 5    | pF    |

| Common Mode Rejection Ratio                        |                                     | CMRR                 |                                                  | 40     | -     | -    | dB    |

| Input Level                                        |                                     | V <sub>IN</sub>      | Differential                                     | -      | -     | 9    | Vp-p  |

| Input Common Mode Voltage                          |                                     | V <sub>ICM</sub>     |                                                  | -10    | -     | +10  | V-pk  |

| Threshold Voltage                                  | Detect                              | V <sub>THD</sub>     | 1 MHz Sine Wave (Measured at                     | 1.2    | -     | 20.0 | Vp-p  |

| (Direct-Coupled)                                   | No Detect                           | V <sub>THND</sub>    | Point "AD" in Figure 6)                          | -      | -     | 0.28 | Vp-p  |

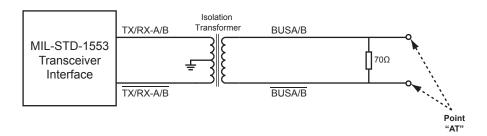

| Threshold Voltage                                  | Detect                              | V <sub>THD</sub>     | 1 MHz Sine Wave (Measured at                     | 0.86   | -     | 14.0 | Vp-p  |

| (Transformer-Coupled)                              | No Detect                           | V <sub>THND</sub>    | Point "AT" in Figure 7)                          | -      | -     | 0.2  | Vp-p  |

| TRANSMITTER (Measured at Po                        | int "AD" in Figure 6 unl            | ess otherwis         | se specified)                                    |        |       |      |       |

|                                                    | Direct Coupled                      | V <sub>out</sub>     | 35Ω Load                                         | 6.0    | 7.0   | 9.0  | Vp-p  |

| Output Voltage                                     | Direct Coupled  Transformer Coupled | V <sub>out</sub>     | 70Ω Load (Measured at Point<br>"AT" in Figure 7) | 20.0   | 22    | 27.0 | Vp-p  |

| Output Noise                                       |                                     | V <sub>on</sub>      | Differential, Direct Coupled                     | -      | -     | 10.0 | mVp-p |

|                                                    | Direct Coupled                      | V <sub>DYN</sub>     | 35Ω Load                                         | -90    | -     | 90   | mV    |

| Output Dynamic Offset Voltage                      | Transformer Coupled                 | V <sub>DYN</sub>     | 70Ω Load (Measured at Point<br>"AT" in Figure 7) | -250   | -     | 250  | mVp   |

| Rise/Fall Time                                     |                                     | t <sub>r/f</sub>     | MIL-STD-1553B compliant                          | 100    | 150   | 300  | ns    |

| Output Resistance                                  | '                                   | R <sub>out</sub>     | Differential, not transmitting                   | 10     | -     | -    | kΩ    |

| Output Capacitance                                 | '                                   | C <sub>out</sub>     | 1 MHz sine wave                                  | -      | -     | 15   | pF    |

| Clock Input                                        |                                     |                      |                                                  |        |       |      |       |

|                                                    | (Default)                           |                      |                                                  |        | 16.0  |      | MHz   |

|                                                    | (option)                            | CLK                  |                                                  |        | 12.0  |      | MHz   |

| Frequency                                          | (option)                            | CLK <sub>IN</sub>    |                                                  |        | 10.0  |      | MHz   |

|                                                    | (option)                            |                      |                                                  |        | 20.0  |      | MHz   |

| MIL-STD-1553 Message Timing                        |                                     |                      |                                                  |        |       |      |       |

| RT-to-RT Response Timeout (mid-parity to mid-sync) |                                     |                      |                                                  | 17.5   | 18.5  | 19.5 | μs    |

| RT Response Time (mid-parity to                    | mid-sync)                           |                      |                                                  | 4      |       | 7    | μs    |

| Transmitter Watchdog Timeout                       |                                     |                      |                                                  |        | 660.5 |      | μs    |

**Note 1:** In actual use, the highest practical transmit duty cycle is 96%, occurring when a Remote Terminal responds to a series of 32 data word transmit commands (RT to BC) repeating with minimum intermessage gap of  $4\mu s$  ( $2\mu s$  dead time) and typical RT response delay of  $5\mu s$ .

**Note 2:** While one bus continuously transmits, the power delivered by the power supply is  $5.0V \times 565mA$  max = 2.825W. Of this, 1.55W is dissipated in the device, the remainder in the load.

#### 5.4. MIL-STD-1553 Bus Interface

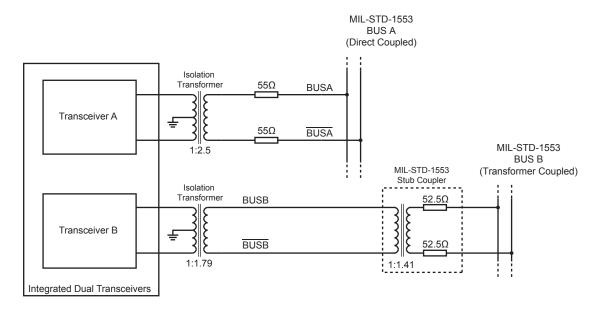

Figure 4. Bus Connection Example (HI-62605CQx, 5.0V transceivers)

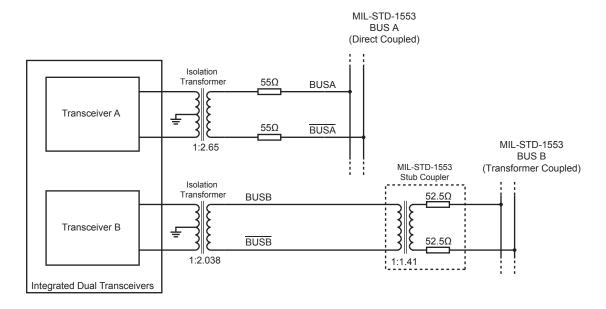

Figure 5. Bus Connection Example (HI-62603CQx, 3.3V transceivers)

## 5.5. MIL-STD-1553 Test Circuits

#### **Each Bus**

Figure 6. MIL-STD-1553 Direct Coupled Test Circuits

## **Each Bus**

Figure 7. MIL-STD-1553 Transformer Coupled Test Circuits

# 6. Package Dimensions

Figure 8. 80-Pin Gull Wing Package Dimensions

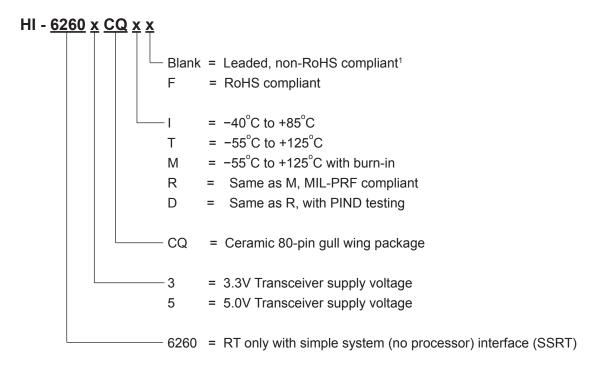

## 7. Ordering Information - 80 Pin Gull Wing Package

Note 1: Solder dipped, Sn/Pb solder

# **Revision History**

# 8. Revision History

| Revision Date             |        | Date     | Description of Change                                                    |

|---------------------------|--------|----------|--------------------------------------------------------------------------|

| DS6260, Rev. New 05/23/18 |        | 05/23/18 | Initial Release                                                          |

| Rev. A 05/23/19           |        | 05/23/19 | Add package photo to title page. Add dimension units to package drawing. |

|                           |        |          | Add more detail to block diagram.                                        |

|                           | Rev. B | 12/20/19 | Add pin diagram and clarify pin descriptions.                            |

|                           |        |          | Other minor updates and corrections.                                     |