HI-8040

CMOS High Voltage Display Driver

March 2007

### **GENERAL DESCRIPTION**

The HI-8040 is a CMOS integrated circuit designed for high voltage LCD display drive applications. It can drive 85 segments at voltages between +5 and -30 volts. An optional voltage converter can generate the negative display drive voltage. Test inputs facilitate opens and shorts testing. The backplane frequency is checked and, as long as power is available, the segments are shut "Off" if the frequency becomes too low.

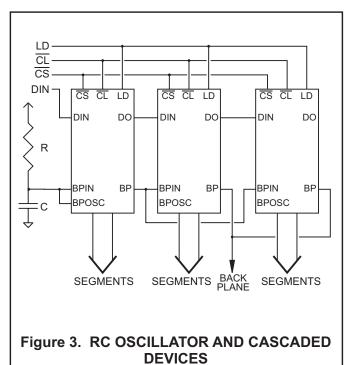

The HI-8040 is part of a family of display drivers which control segment information in the same way. Data is serially clocked into the device and the data for all segment outputs are latched in parallel when the Load input transitions from high to low. With the Data Out from the shift register available, devices may be cascaded to obtain more segment outputs. The shift register is 85 bits long.

The die is metal mask programmable to provide for various package and/or cascade tap options. Consult your Holt Sales representative to explore the possibilities.

### **FEATURES**

- · 4 MHz serial input data rate

- 85 segment outputs

- Cascadable

- 5 Volt inputs translated to 35 Volts

- Test pins allow hardware all "ON", all "OFF" or alternating

- Monitors backplane oscillation and forces all segments to "OFF" condition if below 10Hz

- Negative voltage converter available on-chip

- · CMOS low power

- Military processing available

### **APPLICATIONS**

- Dichroic Liquid Crystal Displays

- Standard Liquid Crystal Displays

- MEMS Drivers

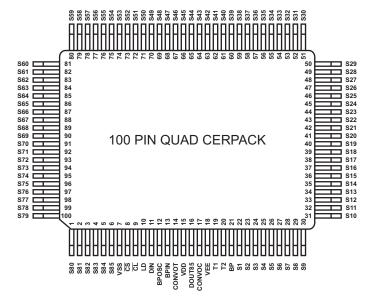

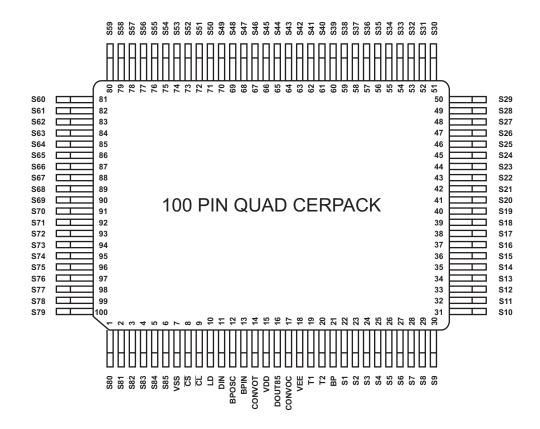

# PIN CONFIGURATION (Top View)

See page 5 for magnified view

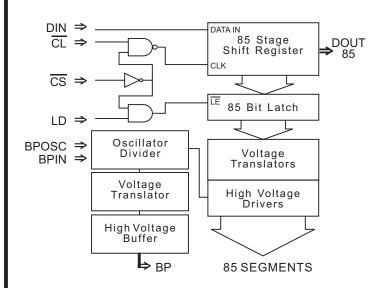

## **FUNCTIONAL BLOCK DIAGRAM**

## **FUNCTIONAL DESCRIPTION**

#### **INPUT LOGIC**

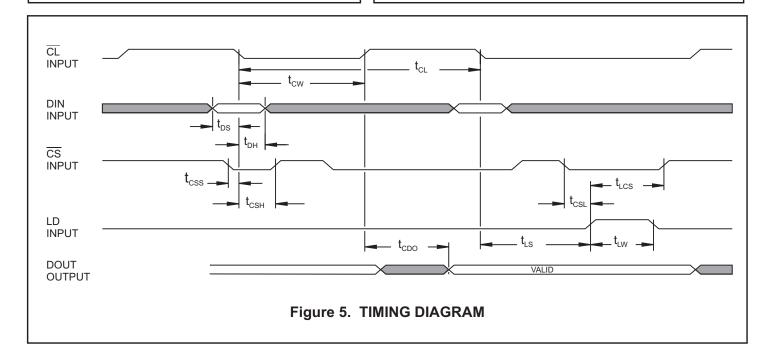

CS must be held low to enter data into the shift register. The data is clocked on the negative edge of CL. LD is normally held low and only pulsed high when new data is ready for display. When LD is high the latch is transparent. All four logic inputs are TTL compatible. A logic "1" at DIN that is eventually latched to the segment drivers will cause the segment to be at the opposite voltage level of the BP pin (out of phase).

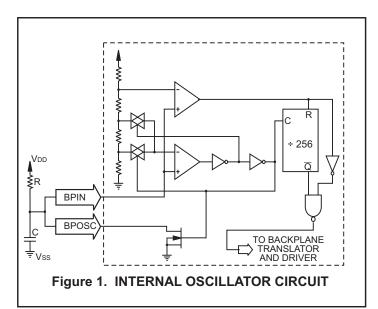

#### **BPOSC and BPIN**

The user can either make an oscillator to create the backplane frequency or drive an external clock into BPIN leaving BPOSC open. To make an oscillator, pins BPOSC and BPIN must be connected together and the appropriate R and C combination applied (See Figure 1). If the oscillator is used, the backplane frequency is approximately

$$f_{BP} = \frac{1}{256 \text{ RC}}$$

(for R = 180K $\Omega$  & C = 220pF,  $f_{BP} \approx 100$ Hz).

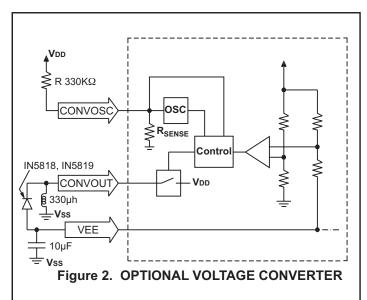

#### **VEE & NEGATIVE VOLTAGE CONVERTER**

VEE may be externally driven to a maximum -30V. Alternatively, there is a voltage converter that will provide -21.4 volts (See Figure 2). If the converter pins are left open circuit, an on-chip sense resistor will cause shut down of all current consumption associated with the converter. The converter will survive a shorted segment condition and continue to maintain VEE at -20 volts.

#### DOUT

The DOUT pin is available from segment 85 for cascading devices to drive more segments and for verifying the data integrity. This output can drive 2 TTL loads. It changes on the positive edge of  $\overline{\text{CL}}$ .

#### **AUTOMATIC SEGMENTS OFF**

The internal backplane signal is tested continuously to be at least 10Hz. If the detector senses f<10Hz, then the segments are forced to the same voltage as the backplane (all segments in "OFF" state). However, the detector is only functional while VDD is above the minimum operating voltage specification.

#### **TEST INPUTS**

The test functions available are:

| <u>T2</u> | <u>T1</u> | <u>Display</u>              |

|-----------|-----------|-----------------------------|

| 0         | 0         | Normal                      |

| 0         | 1         | All Off                     |

| 1         | 0         | All On                      |

| 1         | 1         | Alternating On/Off Segments |

|           |           |                             |

The test inputs must be tied to the appropriate logic level for correct circuit operation.

## **ABSOLUTE MAXIMUM RATINGS**

Voltages referenced to VSS = 0V

| Supply Voltage       |                                             | Power Dissipation300 mW                                             |

|----------------------|---------------------------------------------|---------------------------------------------------------------------|

| Voltage at any input | VEEVDD-35V to 0V except BPIN0.3 to VDD+0.3V |                                                                     |

|                      | utVDD-35 to VDD+0.3V                        | I On a rational Tanana rational Danasa I II Tanan Mil EE9 ta 140E90 |

|                      | ut pin10 mA                                 |                                                                     |

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### DC ELECTRICAL CHARACTERISTICS

$VDD = 5V \pm 5\%$ , VEE = -21.5V, VSS = 0V, TA = operating temperature range (unless otherwise specified).

| PARAMETER                                  | SYMBOL                            | CONDITION | MIN             | TYP     | MAX    | UNITS   |    |

|--------------------------------------------|-----------------------------------|-----------|-----------------|---------|--------|---------|----|

| Operating Voltage                          |                                   | VDD       |                 | 3.0     |        | 7.0     | V  |

| Supply Current: (Conver                    | ter Off, fBP = 100Hz)             | IDD       | Static, No Load |         | 300    | 600     | μA |

|                                            |                                   | IEE       | Static, No Load |         |        | 120     | μA |

| Input Low Voltage                          | nput Low Voltage (excluding BPIN) |           |                 | 0       |        | 0.8     | V  |

| Input High Voltage (excluding BPIN)        |                                   | VIH       |                 | 2       |        | VDD     | V  |

| Input Low Voltage (BPIN)                   |                                   | VILX      |                 | VEE     |        | 0.6 VDD | V  |

| Input High Voltage (BPIN)                  |                                   | VIHX      |                 | 0.8 VDD |        | VDD     | V  |

| Input Current                              |                                   | IIN       | VIN = 0 to 5V   |         |        | 100     | nA |

| Input Capacitance (Guaranteed, not tested) |                                   | CI        |                 |         |        | 5       | pF |

| Segment Output Impedance                   | RSEG                              | IL = 10μA |                 |         | 15,000 | Ω       |    |

| Backplane Output Impedance                 | Backplane Output Impedance        |           |                 |         |        | 600     | Ω  |

| Data Out Current:                          | Source Current                    | IDOH      | VOH = 4.5       |         |        | -3.0    | mA |

|                                            | Sink Current                      | IDOL      | VOL = 0.4       | 3.2     |        |         | mA |

| Voltage Converter:                         | @ No Load                         | VEEc      | See Fig. 2      | -22     | -21.5  | -21     | V  |

| (VDD - VSS = 5V, TA = 25°C                 | @ 0.1mA Load                      | IDD       | See Fig. 2      |         |        | 1.8     | mA |

|                                            | @ 10KΩ Load                       | VEEc      | See Fig. 2      | -20     |        |         | V  |

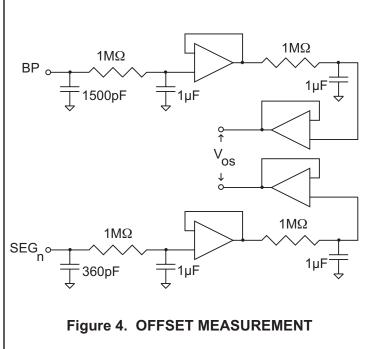

| Offset Voltage (Gu                         | aranteed, not tested)             | VOS       | See Fig. 4      |         |        | 25      | mV |

## **AC ELECTRICAL CHARACTERISTICS**

VDD = 5V, VEE = -21.5V, VSS = 0V, TA = operating temperature range (unless otherwise specified).

| PARAMETER                    |              | SYMBOL | VDD | MIN | TYP | MAX | UNITS |

|------------------------------|--------------|--------|-----|-----|-----|-----|-------|

| Clock Period                 | non-cascaded | tCL    | 5V  | 250 |     |     | ns    |

|                              | cascaded     | tCL    | 5V  | 500 |     |     | ns    |

| Clock Pulse Width            | non-cascaded | tCW    | 5V  | 125 |     |     | ns    |

|                              | cascaded     | tCW    | 5V  | 250 |     |     | ns    |

| Data In - Setup              |              | tDS    | 5V  | 80  |     |     | ns    |

| Data In - Hold               |              | tDH    | 5V  | 80  |     |     | ns    |

| Chip Select - Setup to Clock |              | tCSS   | 5V  | 100 |     |     | ns    |

| Chip Select - Hold to Clock  |              | tCSH   | 5V  | 120 |     |     | ns    |

| Load - Setup to Clock        |              | tLS    | 5V  | 120 |     |     | ns    |

| Chip Select - Setup to Load  |              | tCSL   | 5V  | 0   |     |     | ns    |

| Load Pulse Width             |              | tLW    | 5V  | 130 |     |     | ns    |

| Chip Select - Hold to Load   |              | tLCS   | 5V  | 120 |     |     | ns    |

| Data Out Valid, from Clock   |              | tCDO   | 5V  |     |     | 170 | ns    |

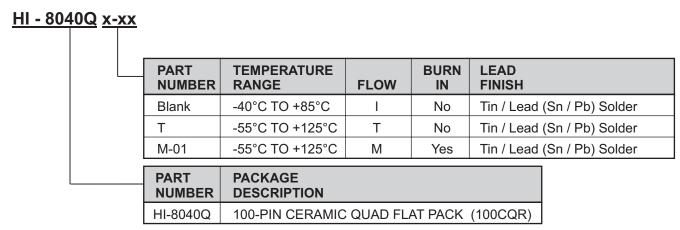

## **ORDERING INFORMATION**

Note: No lead-free RoHS compatible option for this package.

## **PIN ASSIGNMENTS**

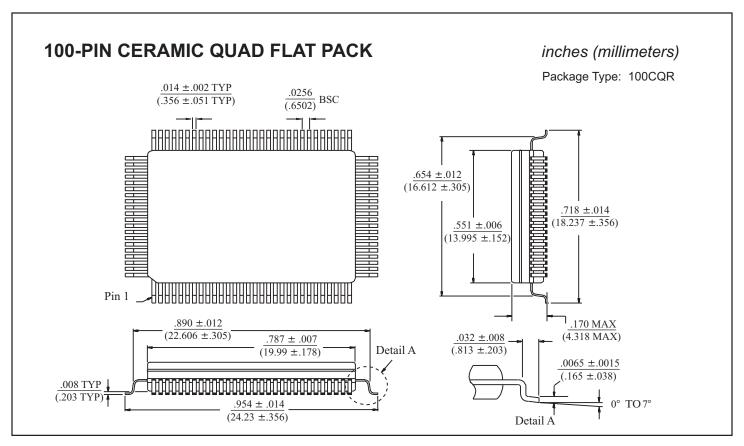

# HI-8040 PACKAGE DIMENSIONS

BSC = "Basic Spacing between Centers" is theoretical true position dimension and has no tolerance. (JEDEC Standard 95)